논리 설계 24 ( Register , Counter )

asynchronous Counter = 지금 결과가 다음 F/F의 CLK이 된다. (asy..에 a가 있으니까 and가 안 나옴)

--> UP counter = 지금 결과의 inversion이 다음 F/F의 CLK

--> Down counter = 지금 결과가 다음 F/F의 CLK

★ [ Input 1을 공유 / CLK은 공유 X ]

synchronous Counter = CLK은 동일하게 공유 (이름에 a가 없으니까 and가 필요함)

--> UP counter = n번째 input은 [ 1~n-1 번째 결과가 모두 1일 때 ] 1

--> Down counter = n번째 input은 [ 1~n-1 번째 결과의 inversion 이 모두 1일 때 ] 1

★ [ CLK 를 공유 / Input은 공유 X ]

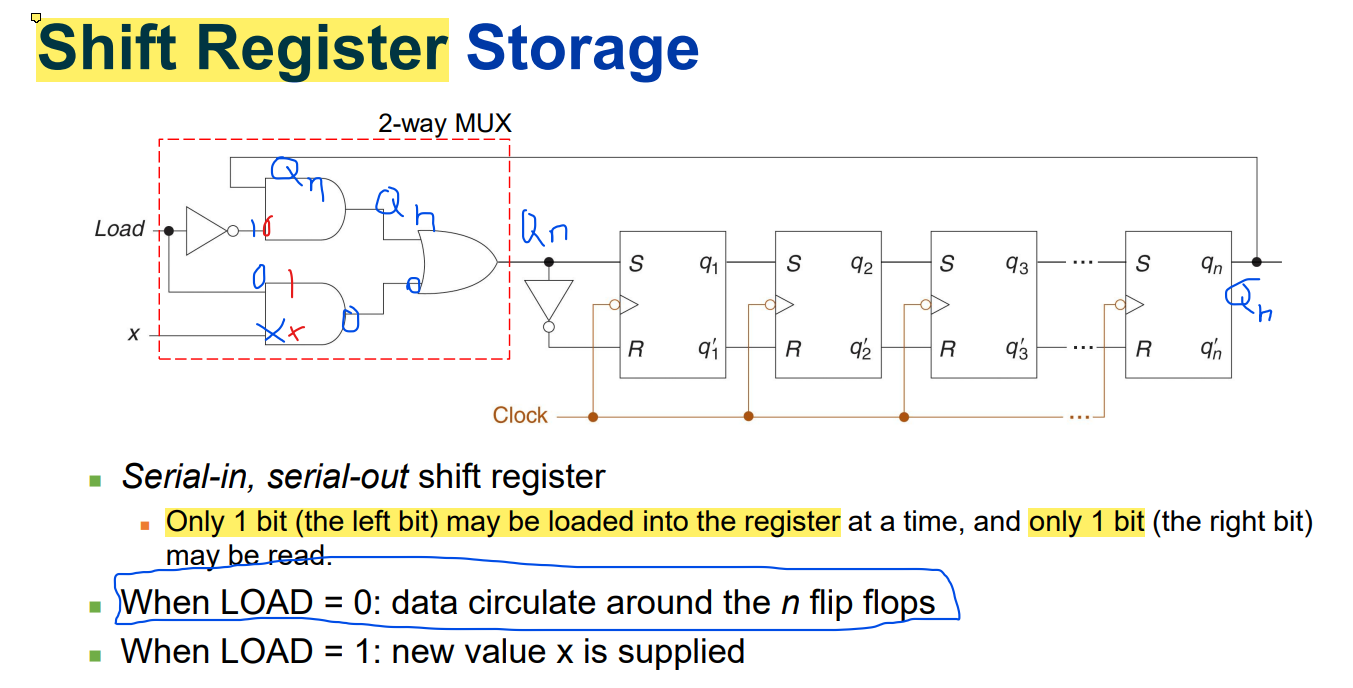

Load가 0이면, 새로운 데이터를 데려오지 않겠다는 의미이다.

그렇게 될 경우에는 위 and게이트가 작동하고 출력된 qn이 다시 입력으로 들어간다.

0001 이었으면, 가장 오른쪽에 있던 애가 circulate 하게 되는 거니까 1000임.

(그냥 제일 끝에 있는 애를 계속 앞으로 데려와서 밀어넣기 한다고 생각하면 쉽다)

또는 Load가 1이면 입력했던 x가 왼쪽에서 밀고 들어감.

이건 CLK 때마다 하나씩 하나씩 받음.

모든 게 0이고 A와 B가 한 번만 1이고 그 뒤로 둘 다 1이 아닐 경우에는

시작 : 00000000 < 1받음

다음 클락 : 10000000 < 이제 바뀜, 근데 들어오는 건 0 인데 1이 있는 그 다음 F/F은 edge에서 1을 받을 준비

그 다음 클락 : 01000000

그 다음 클락 : 00100000 ...

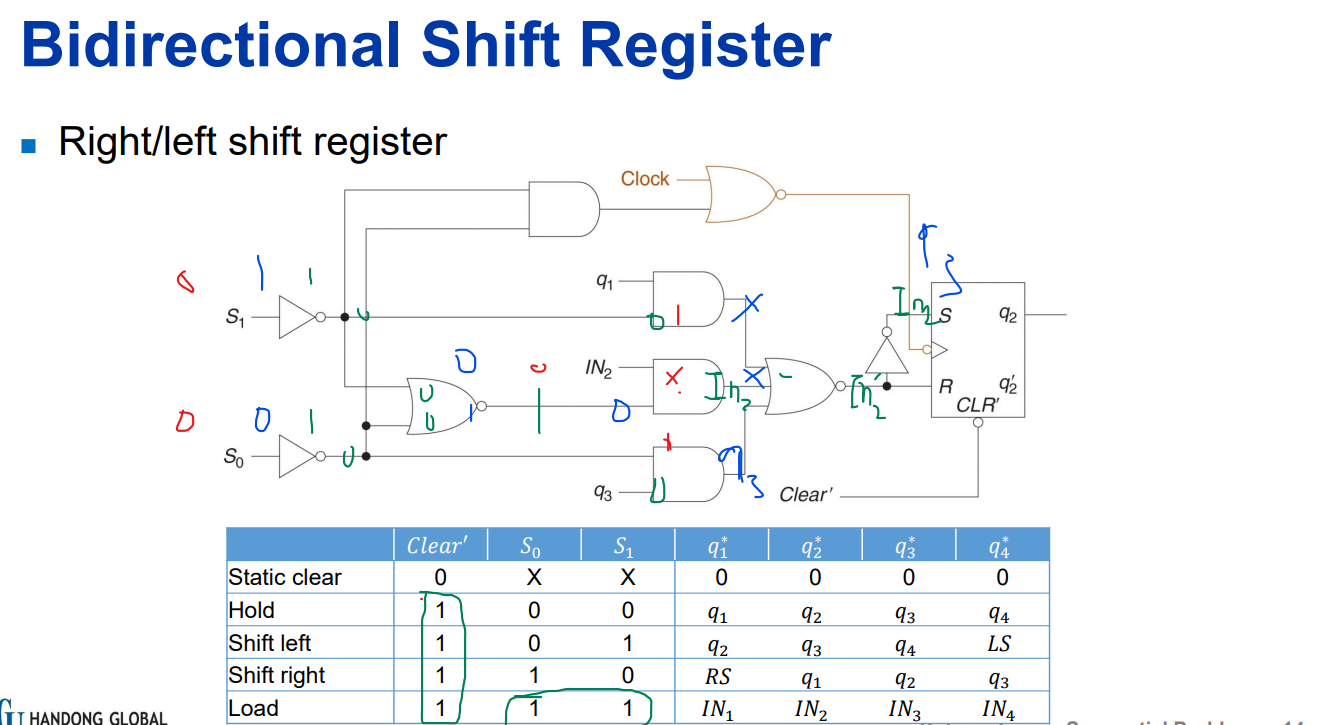

S0 = Shift right

S1 = Shift left라고 보면 됨.

S0이 1이면 q1* 은 RS의 값이 들어간다.

-------------------------

S0,S1둘 다 0이면 --> CLK이 0이므로 그냥 원래 상태 유지 (HOLD)

S0 = 0 / S1 =1 이면 --> q1이 있는 and게이트는 작동하지 않고, q3가 있는 and게이트만 작동한다.

그럼 q2에는 q3가 들어간다는 거니까, LS라고 생각하면 됨 (뒤에서 뭐가 밀려왔다)

S0 = 1 / S1 =0 이면 --> q1이 있는 and게이트는 작동하고, q3가 있는 and게이트는 작동하지 않는다.

그럼 q2에는 q1이 들어간다는 거니까, RS라고 생각하면 됨 (앞에서 뭐가 밀려왔다)

Counter

Upcounter : Negative edge trigger

Downcounter : Positive edge trigger

8개의 숫자를 나타내고 0부터 7까지 상승하는 counter를 보자.

Up counter는 0부터 7까지 올라가는 counter이다.

asynchronous 이므로 앞 결과가 다음 F/F의 CLK이 된다.

( Q1이 [ 0>1로 바뀔 때 or 1>0으로 바뀔 때 ] Q0 은 1>0으로 바뀐다.

--> Qn 이 (어떤 형태로든) 바뀔 때, Qn-1은 1>0으로 바뀐다. )

※ Up counter는 앞 비트 결과의 반대가 CLK이 됨

※ Down counter는 앞 비트 결과가 CLK이 됨

7>0 으로 가는 싸이클을 돈다.

위에서 F/F의 결과가 다음 F/F의 CLK이 될 경우에 Delay가 쌓이고 쌓인다.

첫 번째 결과 나올 때 까지 걸리는 시간 + 두 번째 결과 ...+ n 번째이므로

비트 수가 커지면 커질수록 비효율적이다.

Q1이 [ 0>1로 바뀔 때 or 1>0으로 바뀔 때 ] Q0 은 1>0으로 바뀐다. (toggle 된다)

--> Qn 이 (어떤 형태로든) 바뀔 때, Qn-1은 1>0으로 바뀐다. (toggle 된다)

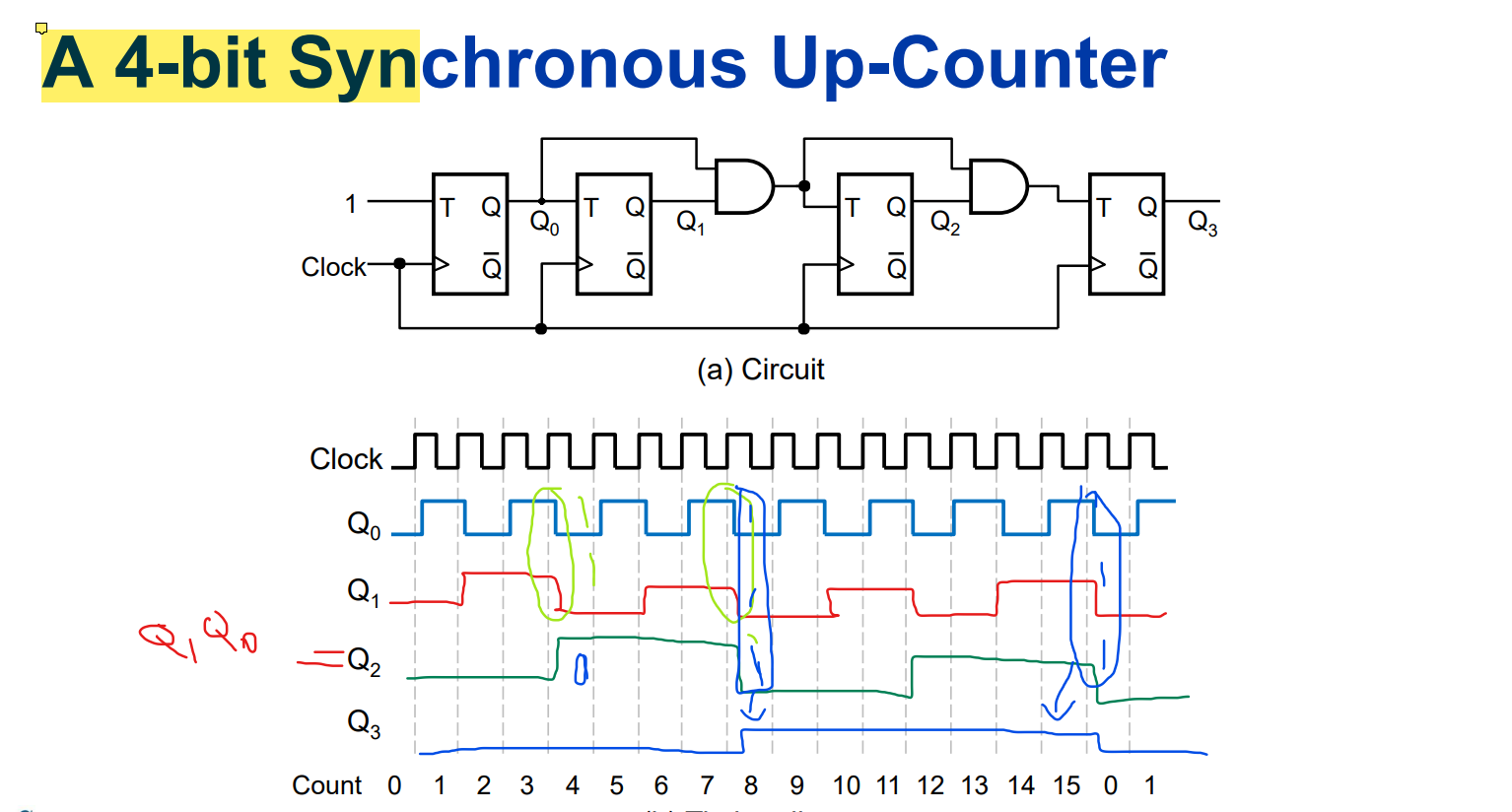

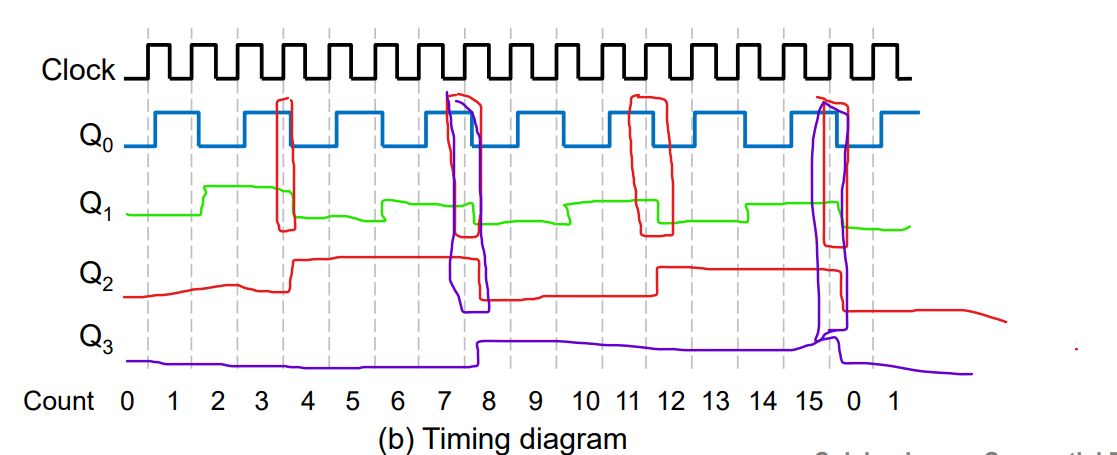

+ Qn 보다 작은 비트들이 모두 다 1이면,

다음 상태는 Qn가 Toggle됨 (나머지들은 0이 됨.)

설명할 건 회로밖에 없을 듯 하다.

And가 있는 이유는

[ Qn 보다 작은 비트들이 모두 다 1이면, 다음 상태는 Qn가 Toggle됨 (나머지들은 0이 됨.) ] <<이거 때문이다.

앞 두 개(n-1개) 가 모두 1이어야 T에 1이 들어가서 작동함.

Q2는 Q1,Q0 둘 다 1일 때 T가 작동

Q3는 Q2,Q1,Q0 셋 다 1일 때 T가 작동한다.

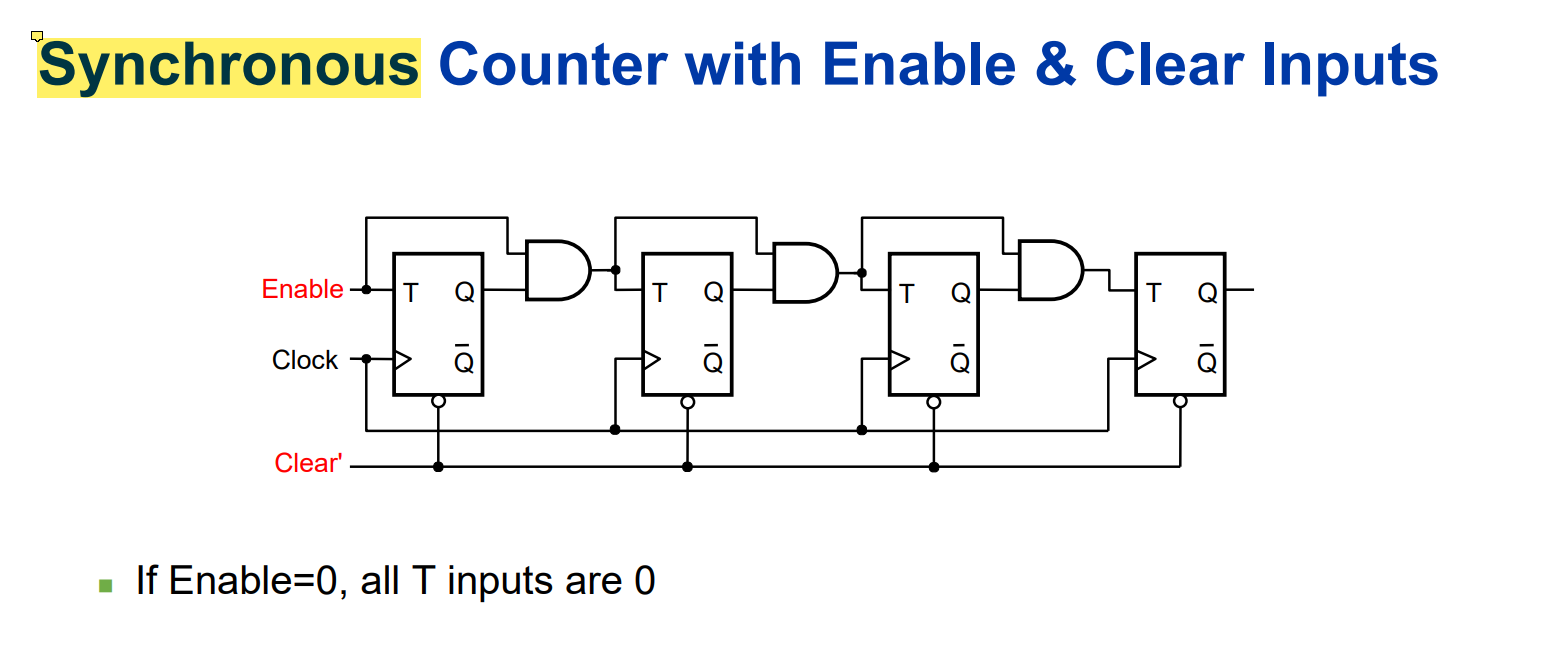

방금 위에 나온 Circuit에서 Enable만 붙은 거임.

Enable이 0이면 T에 아무 것도 안 들어간다.

이 circuit에서 1 대신 enable을 넣고 and게이트들에 같이 이어줬다고 보면 된다.

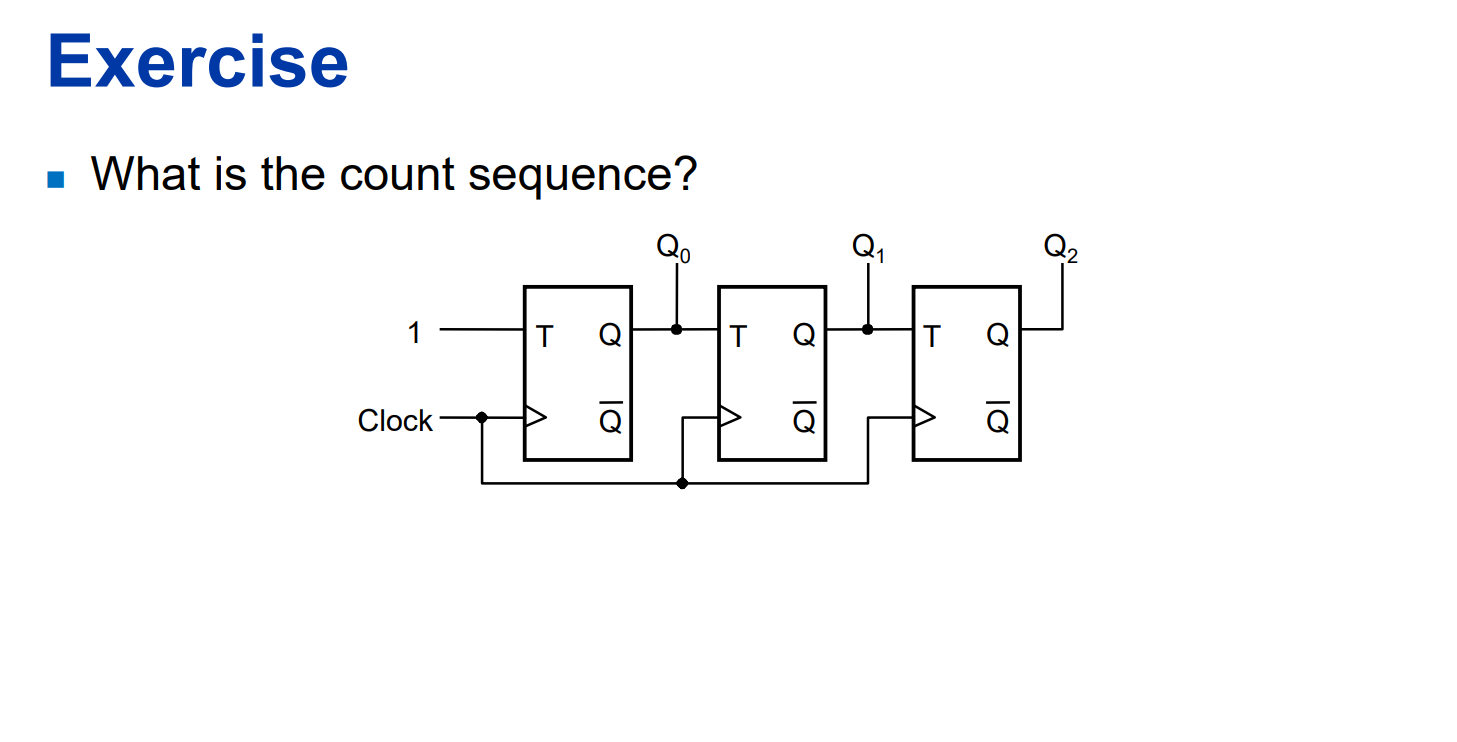

CLK은 같이 받고, T의 입력은 앞 F/F의 결과이다.

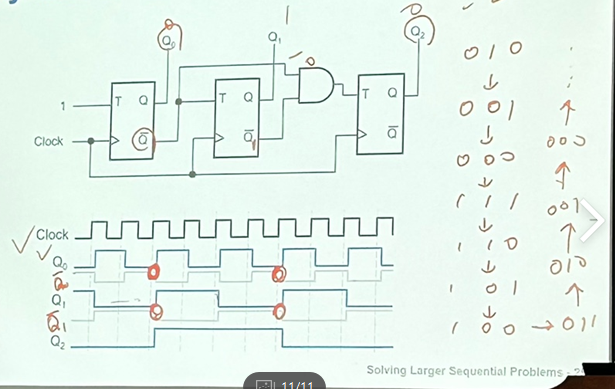

000 > 001 > 010 > 111 > 000 > 반복...

ㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡ

010 > 001 > 000 > 111 > 110 > 101 > 100 > 011 > 010 > 반복...

출처 : 한동대학교 고윤민교수님 - 논리설계 PPT