오래 못 할 짓 하지 않기

[ 컴퓨터 구조 ] 11. Pipeline DataPath 본문

Pipeline DataPath

Pipeline에 Hazards가 없다고 가정하고 Datapath를 설계할 예정이다.

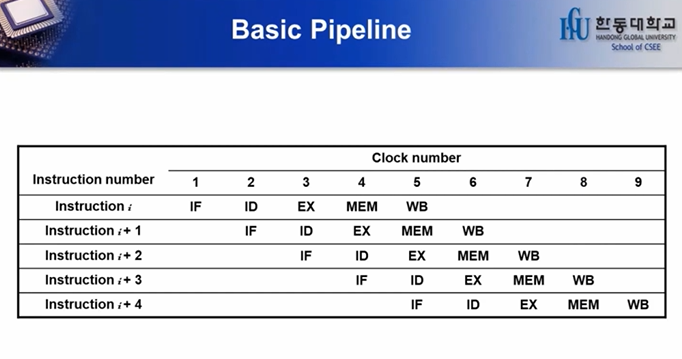

정확히 Pipeline의 모양은 이렇다.

돌림노래라고 생각하면 가장 이해하기 쉬울 듯.

5번째 CLK일 때(부터), 5개의 명령어가 Pipeline 꽉꽉 채워서 다 돌아감

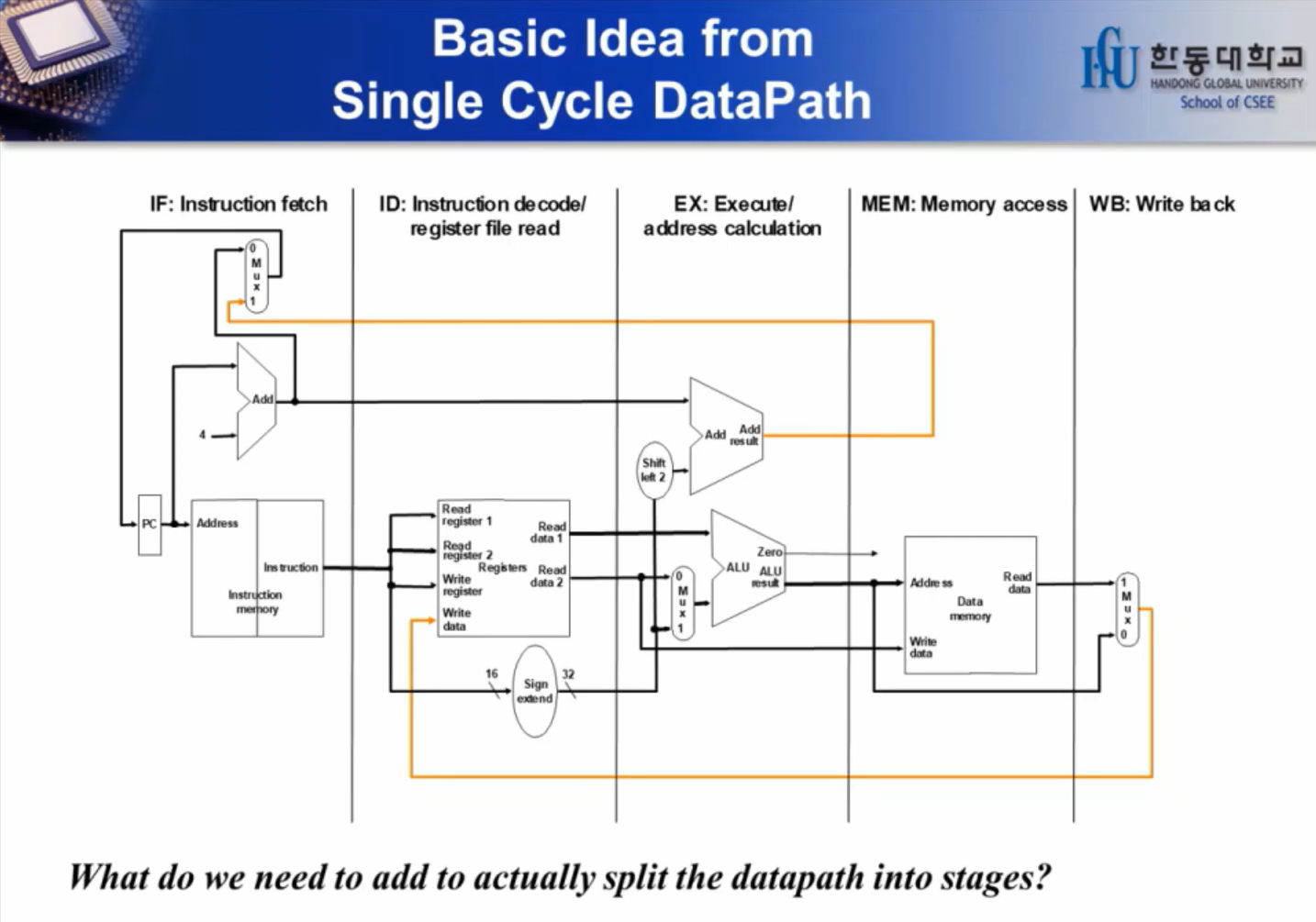

Single Cycle Datapath를 Pipeline 5 steps에 맞춰 나누었음.

IF = PC , Instruction memory 를 이용하여 instruction을 가져온다.

ID = Register file 를 읽는다.

EX = ALU 로 연산을 한다.

MEM = Memory 에 access한다.

WB = Memory 혹은 ALU에서 나온 값을 받아서 Register file로 back한다.

중요한 점은, 이 step들이 동시에 작동은 하되, 데이터들이 섞이지 않도록 해야 한다.

따라서 이 Pipeline들을 나누어주는 Register가 필요하다.

IF/ID 라고 되어있으면 그 Register 기준으로 왼쪽이 IF , 오른쪽이 ID라는 뜻.

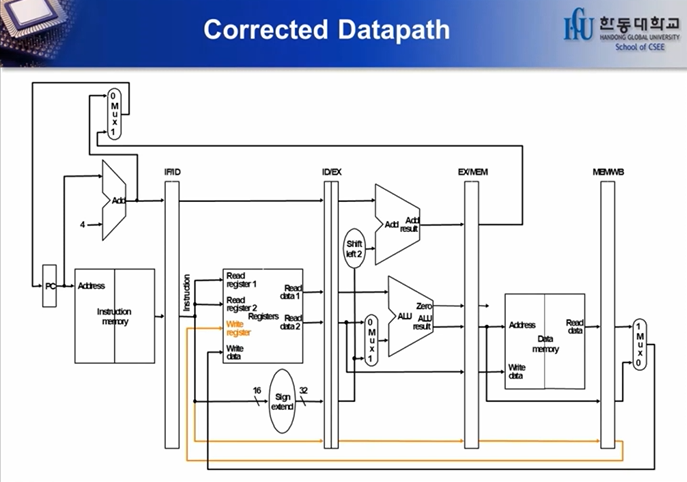

이 구조의 치명적인 단점 : LW 는 Write register 위치에 적힌다. ALU에서 연산한 값이 Data memory 의 주소로 들어가고

그 값이 나오면서 Write data로 들어간다.

근데 Write Register가 주는 주소는 어떻게 될까? 이전 구조였으면 얜 한 번 Instruction을 받고 놀고 있다가 오면 작업을 했었는데, 이젠 놀고 있는 게 아니라 일이 있는 애다.

아래가 그 해결법이다.

LW 의 목적지 register ( rt ) 도 Pipeline에서 연산을 같이 하지는 않고 write 될 때까지 같이 따라다니게 된다.

출처 : 한동대 SW중심대학

'2학년 2학기 > 컴퓨터 구조' 카테고리의 다른 글

| [ 컴퓨터 구조 ] 13. Data Hazard (0) | 2023.07.07 |

|---|---|

| [ 컴퓨터 구조 ] 12. Pipeline 제어부 (Control) (0) | 2023.07.07 |

| [ 컴퓨터 구조 ] 10. Pipeline 적용 (0) | 2023.07.06 |

| [ 컴퓨터 구조 ] 9. Pipeline (0) | 2023.07.05 |

| [ 컴퓨터 구조 ] 8. (Multiple Cycle) Multiple Cycle 제어부 (Control Unit) (0) | 2023.07.05 |