오래 못 할 짓 하지 않기

[ 컴퓨터 구조 ] 3. Instruction Set Completeness 본문

Instruction은 Completeness 가 있어야 한다.

: 뭐 하나 빼먹으면 작동 안 하고, 다 complete 해야 원하는대로 작동한다 이말

아래 3개 중에 하나라도 없으면 Complete 하다고 할 수 X

Instruction은 아래 3가지를 다루어야 한다.

● Arithmetic / Logical ▶ 연산을 한다거나

ex) 데이터 값을 수정 및 연산 + - * /

● Data Transfer ( including I/O ) ▶ 데이터를 가공한다거나

ex) 데이터를 한 곳에서 다른 곳으로 복사

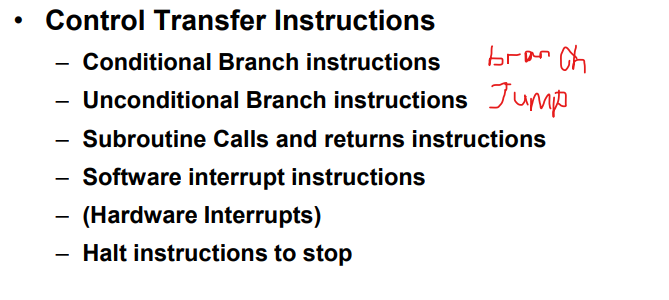

● Control Transfer ▶ Branch나 조건부 조절을 해야한다!

ex) Jump (조건부X) or Branch (조건부)그럼 아래에서 각각 더 자세히 알아보자

Arithmetic / Logical Inst (Data Operations)

- (Integer) Arithmetic Operations

ex) + - * / ++ or - -

- Logical operations

Bitwise And , Or

Complement

- Shift instructions

- Logic shift

- Arithmetic shift

- Rotate

ex) 1010 에서 <로 한 칸씩 이동시키면

010X 이다. 그럼 여기에서 X를 어떻게 채울까?

1) Logic shift : 0으로 채움 → 0100

2) Rotate ( circular shift ) : 나간 놈으로 데려옴 → 0101

3) Artithmetic shift

:근본적으로 shift 가 *2나 /2임

단, negative 숫자면 가장 앞 비트 숫자는 냅두고 하고,

다른 걸 이동시킨 뒤에 빈 칸은 *2나 /2가 되도록 하는 숫자로 넣는다

(그냥 알아만 두라 함) 결과에 맞게 '숫자를 데려온다' 정도만 알아두기

- Completeness and Orthogonality

위에서 말했듯 Completeness 는 3가지를 다룬다.

1) Arithmetic/Logical Inst

2) Data transfer

3) Control transfer

1. Arithmetic/Logical Inst

● Arithmetic Instructions

1) ADD , SUB, MUL, DIV : 우리가 최소한으로 가장 필요한 단위는 'ADD'랑 'COMP' 이다.

COMP = complement : 보수 개념으로, ADD를 이용하여 뺄셈을 연산한다.

'R(educed)ISC' 에서는 add 와 comp로만 만들 수 있음

( 다른 게 없다는 게 아니다, 두 개로도 구현이 된다는 뜻)

'C(omplex)ISC' 에서는 웬만한 거 다 넣음 그렇다 해도 성능이 좋아지는 건 아니다.

오히려 더 고려해야하고 delay 시켜야하는 게 많아서 더 저하될 수도 있다~!

2) 정수 연산 / 소수점 연산 : 소수점 연산은 정수 연산과 같은 방식으로 작동한다.• Logical Instructions

1) AND, OR, NOT, etc : smallest set is [ 'And / not' ] or [ 'or / not' ]

양쪽 다 Not이 필요한 이유 - 드모르간 법칙 쓰면 서로의 역할을 할 수 있기 때문에완성도 있게 각 연산마다 저것들만 있으면 성능에 상관없이 구현은 가능하다 이 말임.

CISC 가 기능적으로는 훨씬 더 많다. 따라서 Inst의 개수를 줄일 수는 있다.

→ 하지만, op code 에 관한 bit와 hardware를 더 설정해야함.

→ op code bit가 더 많으면, 그걸 읽는 시간이 더 걸리므로, propagation delay 이 생긴다.

ex) CPU clock cycles = inst count * CPI [ 숫자 4로 20만들기 ]

- CISC : MUL 4,5 = Inst count =1개

- RISC : ADD 4 = Inst count =5개

→ RISC에도 MUL이 있을 수 있는데 예시를 들기 위해 이렇게 했다.

2. Data transfer

데이터 이동에는 4가지가 있다.

Load / Store / Move / [ I / O ]

1) Load : 데이터를 메모리에서 Processor로 (여기에서 프로세서는 어떤 걸로 연산하냐에 따라 다르다)

ex) Memory to Register

2) Store : 데이터를 Processor에서 memory로

ex) Register to Memory

3) Move(복사) : 데이터를 Processor 내에서 이동

ex) 데이터를 Register에서 다른 Register로 이동

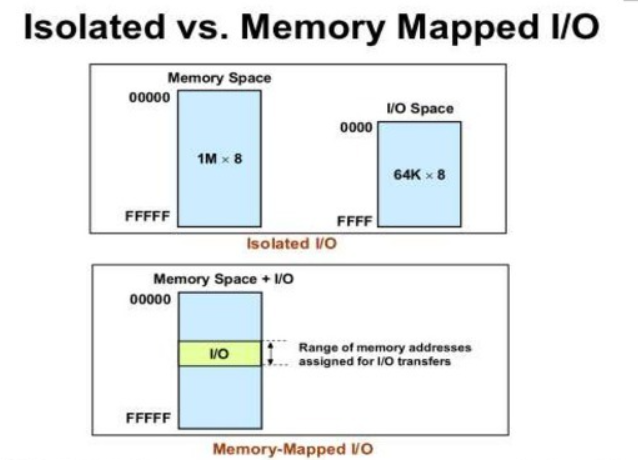

4) Special Inst (File I/O) : [ In / Out을 받을 기기 ] ↔ [ Processor ] 사이에서 작동

- memory mapped I/O

메모리와 I/O가 하나의 연속된 address 영역에 할당된다.

주소에 일부분이 I/O 디바이스에 할당되고,

이 주소들은 I/O 디바이스에 명령어처럼 인식되어 읽고 적을 수 있게 된다.

3. 제어 및 이동

- 연습 문제

completeness : 주어진 작업을 하기 위해 필요한 재료들이 다 갖추어져 있는가에 대한 여부

Orthogonality : 시스템의 견고성과 확장 가능성을 높일 수 있는지에 대한 것 , 겹치거나 필요없는 건 굳이 넣지 마라 이런 느낌임

( 그냥 일단 다 갖고 와 필요할 때가 있을거야 같은 느낌)

2진법

2진수 덧셈 뺄셈하는 법 + 바꾸는 법 정도는 알기

(출처)

한동대학교 용환기 교수님 - 컴퓨터구조 ppt

'2학년 2학기 > 컴퓨터 구조' 카테고리의 다른 글

| 컴구 quiz 대비 (0) | 2023.09.21 |

|---|---|

| [ 컴퓨터 구조 ] 4. MIPS 에 관하여 (0) | 2023.09.17 |

| [ 컴퓨터 구조 ] 2. Addressing Mode (0) | 2023.09.07 |

| 컴퓨터 구조 1 (0) | 2023.09.01 |

| [ 컴퓨터 구조 ] 16. (Hazard) Flushing logic (0) | 2023.07.11 |