오래 못 할 짓 하지 않기

[ 컴퓨터 구조 ] 12주차 makeup 문제 본문

예제 1)

CLK Cycle이 5번째 일 때

각 Control signal이 어떤 상태일지 생각해보기

먼저, 각 Stage에 무슨 명령어가 있는지 파악하는 게 중요한다.

그런 다음에 그 명령어에 필요한 Control signal을 넣어줌.

- RegDst : add 에서 Dst주소는 Instruction 15~11에 있음 : 1

- ALUSrc : 레지스터에서 읽은 값을 ALU에 넣을거라서 0

- MemRead : LW 명령어니까 1

- MemWrite : LW 명령이니까 0

- MemtoReg : LW 명령어니까 1

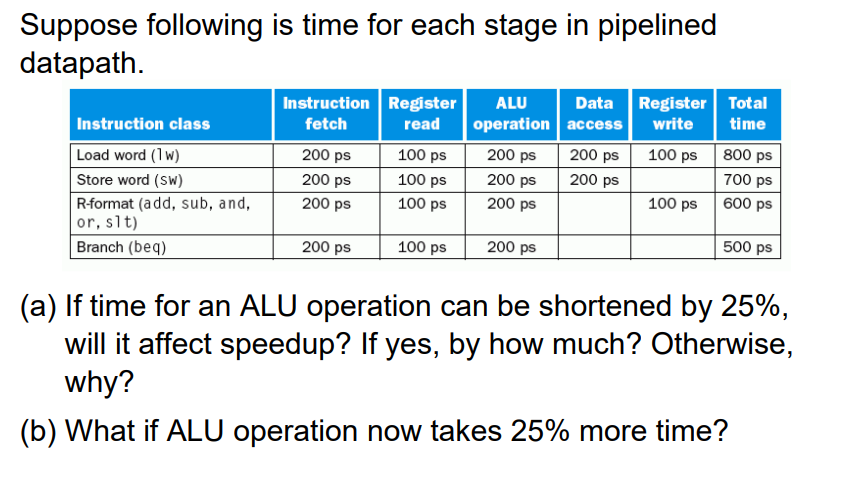

예제2)

a) ALU 작동 시간이 25% 줄어들면 Speedup에 영향이 갈까? 간다면 얼마나 갈까?

→ CLK Cycle은 모든 stage를 통틀어 가장 오래 걸리는 곳에 맞춘다.

ALU를 포함한 3개의 stage가 200ps가 걸림

ALU가 25%줄어 150ps가 걸린다고 해도 다른 stage에서 200ps가 걸리기 때문에 CLK cycle이 줄어들지는 않는다.

= 영향 X

b) ALU 작동 시간이 25% 늘어난다면?

→ 25% 늘어난 시간은 250ps가 된다. 모든 stage 중에서 가장 큰 시간을 차지하므로 speedup에 영향을 준다.

늘어나기 전) ㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡ

PIPEline CLK cycle : 200ps * 5stage

Single : CLK Cycle : 800 ps

CLK cycle 대로 비교하면

800 / 200 =4

늘어난 후)ㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡ

ALU 에 걸리는 시간이 250으로 늘어나면,

850 / 250 = 3.4

Performance가 떨어졌다.

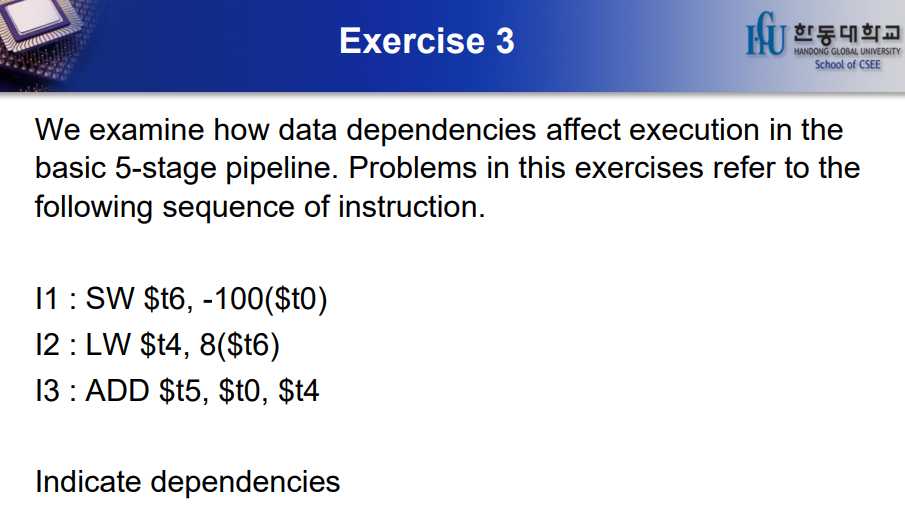

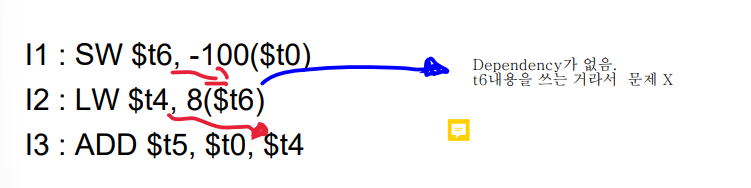

예제3)

Data dependency가 있는지 찾아라.

여기서 낚시는 SW임.

저기에서 $t6를 $t0 -100인 주소에 쓴다는 것이라서 $t6의 값은 변화가 없다.

따라서 I1에 있는 $t6와 I2의 $t6는 Data dependency가 없다.

I2에서 $t4에 값을 알려면 MEM 단계, 값을 저장하려면 WB단계까지 가야한다.

하지만 I3에서 ADD할 때 $t4를 사용하려면 좀 더 기다려야한다. 따라서 둘은 Data dependency가 있다.

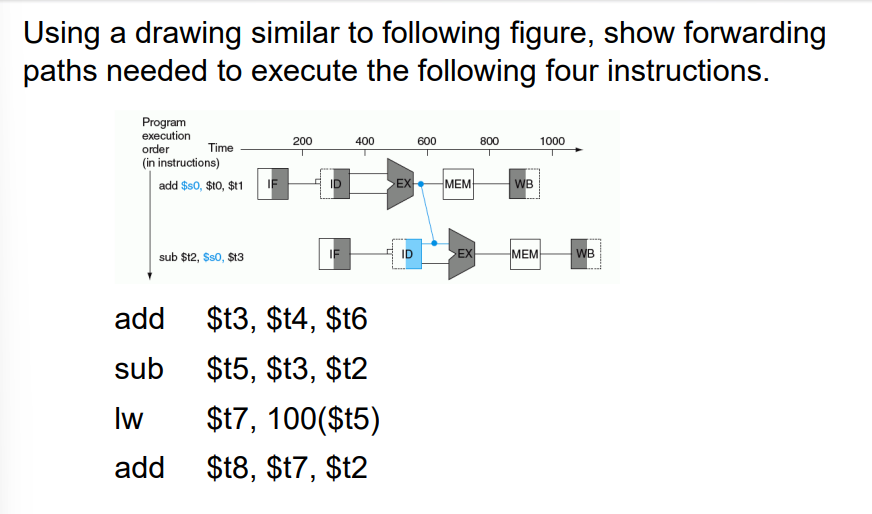

예제 4)

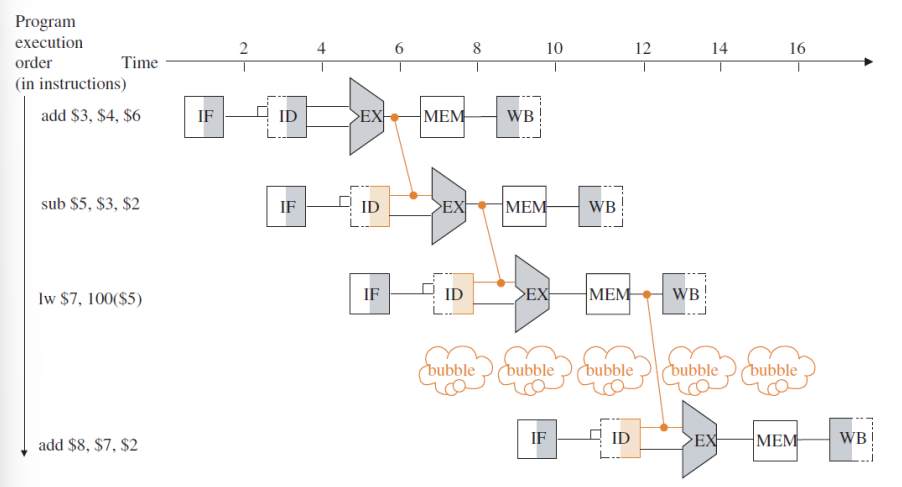

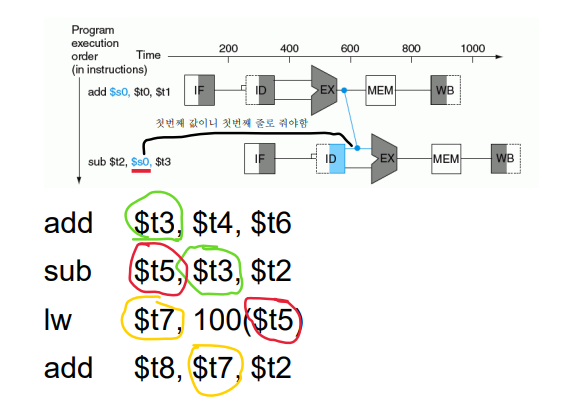

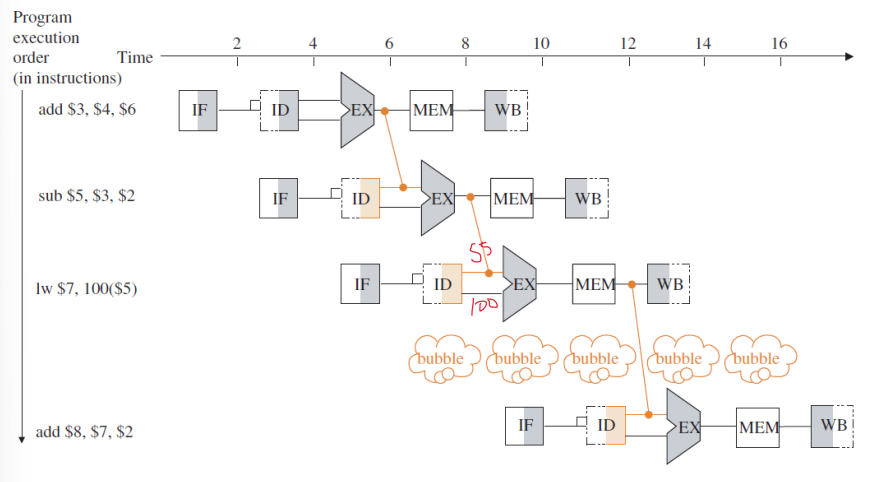

Fowarding 그림 그리기 문제

Register에 값이 들어가서 다음 명령어에 쓰는 걸로 하기엔 너무 길다.

따라서 그 값이 계산되어 나오는 곳에서 기다리고 있다가

다음 명령어에서 해당 값이 필요한 곳에 넣어준다.

여기에서 테스트 하려고 하는 건

1) rs는 첫 번째 줄로 주는 것

2) LW는 MEM에서 나오는데 그 다음 명령어랑은 2단계 차이가 나기 때문에 bubble하기

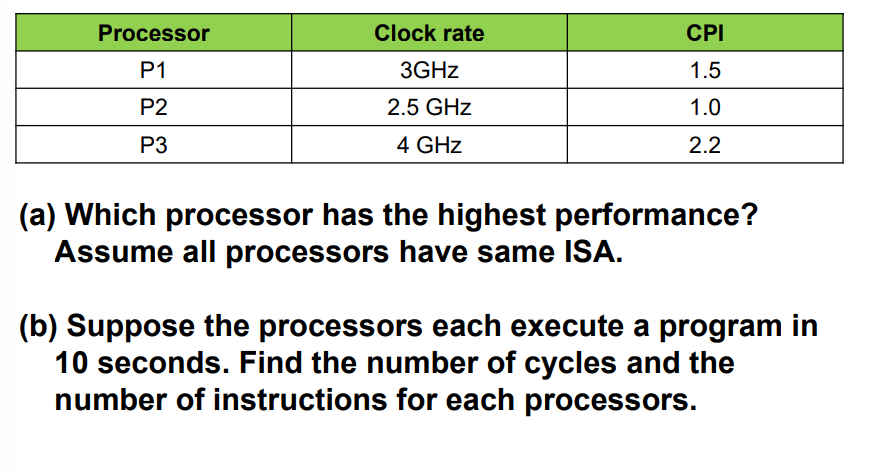

예제 5)

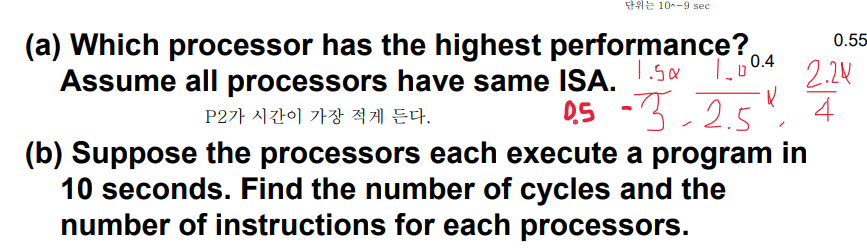

a) 모든 것의 Clock cycle time을 구해보자.

CPU time = CPI * ISA / Clock rate

P1 = 1.5 * a / 3GHz

P2 = 1.0 * a / 2.5GHz

P3 = 2.2 * a / 4GHz

→ P1,P3는 반 이상은 넘기때문에 값이 크다.

Clock cycle time은 짧을수록 performance가 높기때문에 가장 작은 P2가 시간이 가장 적게 든다.

-- b문제는 10초동안 실행되는 명령어의 개수를 물어보는 거임.

b)

1GHZ = 10^9 cycle이 돈다.

Cycle :

10초 동안 몇 개의 Cycle이 돌아가는지

=@ GHz * 시간

- 3GHz * 10초 = 3* 10(초) * 10^9

- 2.5GHz * 10초 = 2.5* 10(초) * 10^9

- 4GHz * 10초 = 4* 10(초) * 10^9

Inst :

10초 동안 몇 개의 Inst를 할 수 있는지

= 주어진 시간 / 명령어 하나당 걸리는 시간

= @GHz * 시간 / CPI

- 3*10^10 cycle /1.5CPI = 2*10^10 inst

- 2.5 * 10^10 cycle / 1.0 = 2.5

- 4* 10^10 cycle / 2.2 = 1.82*10^10

'2학년 2학기 > 컴퓨터 구조' 카테고리의 다른 글

| [ 컴퓨터 구조 ] 22. Cache performance (0) | 2023.11.26 |

|---|---|

| [ 컴퓨터 구조 ] 21. Direct ( cache ) (0) | 2023.11.20 |

| [ 컴퓨터 구조 ] 20. RISC : CISC (0) | 2023.11.13 |

| [ 컴퓨터 구조 ] 19. Performance (0) | 2023.11.12 |

| [ 컴퓨터 구조 ] 11주차 makeup 문제 (0) | 2023.11.11 |