오래 못 할 짓 하지 않기

논리 설계 23 (Asynchronous Counter , Register) 본문

synchronous Counter(살짝)

이걸 풀 때, 진리표, 카르노 맵을 다 만들어서 식을 구한 뒤에

사이클에 없는 0 3 4를 더하고 싶다면 각 비트별로 나온 JK결과들을 사용하여 다이어그램에 추가할 수 있다.

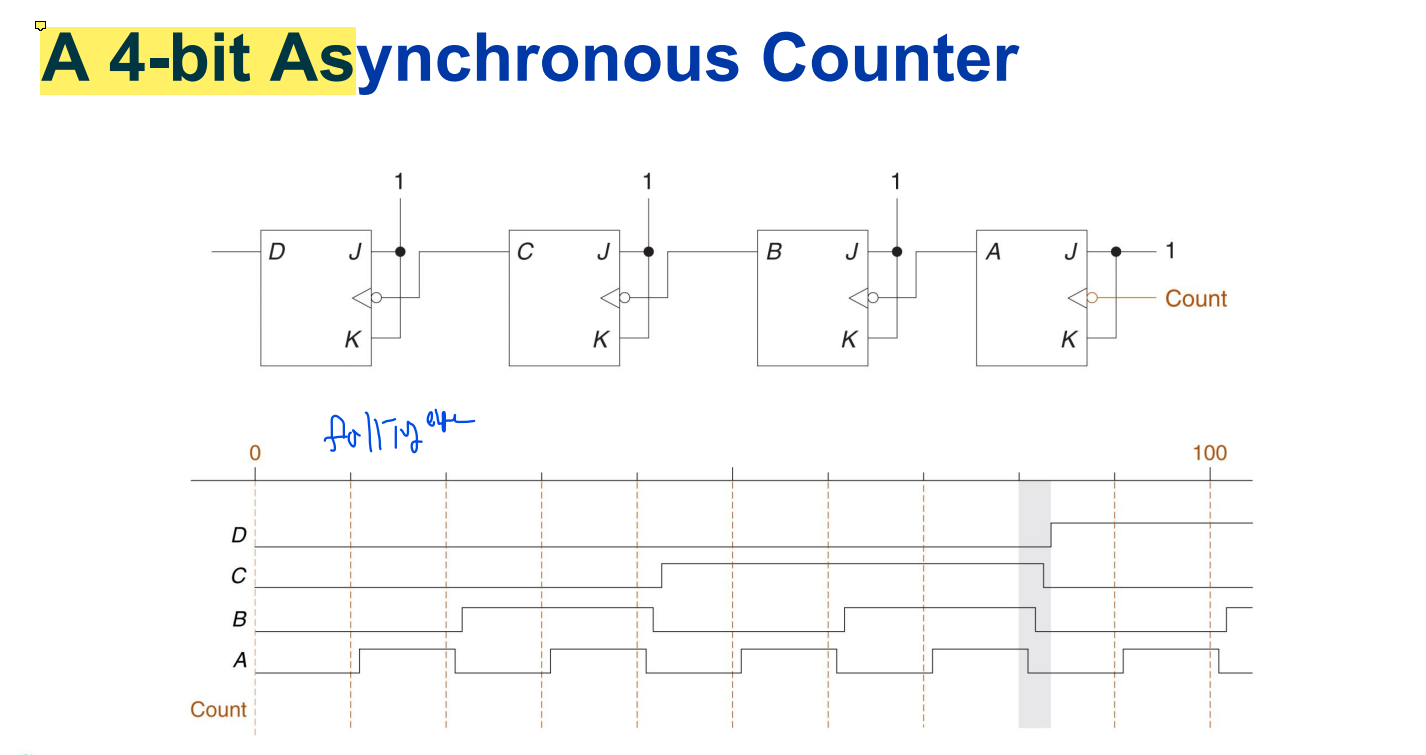

Asynchronous Counter

A의 아웃풋이 Count로 작용함.

B에게는 A의 아웃풋이 Count가 됨

그래서 Asunchronous임. 다 같이 CLK 같은 걸 받으면 같이 동시에 딱딱 변하는데 다른 F/F의 결과를 CLK으로 받으니까 같이 안 변함

Count = CLK 인데 신호가 regular 하지 않음.

circuit을 먼저 보면 모든 J와 K에 1이 들어가므로 Toggle이 됨

모든 Falling egde에서 우선, 가장 앞에 있는 A가 Toggle 된다.

그다음엔 A의 Falling edge에서 B가 Toggle

그다음엔 B의 Falling edge에서 C가 Toggle

그다음엔 C의 Falling edge에서 D가 Toggle

위 Timing diagram에서 끝쪽에 회색으로 된 부분을 한 번 보자.

다 변하는데, A > B > C > D 순서임.

A가 변해야 B가 변하는데 그 사이 Delay가 있음 [ A-B delay ] 가 걸림

B가 변해야 C가 변하는데 그 사이 Delay가 있음 [ A-B delay + B-C dalay ] 가 걸림

C가 변해야 D가 변하는데 그 사이 Delay가 있음 [ A-B delay + B-C dalay + C-D dalay ] 가 걸림

각 비트별로 숫자는 내가 그래프 0000,0001 하는 거라고 생각할 수 있음

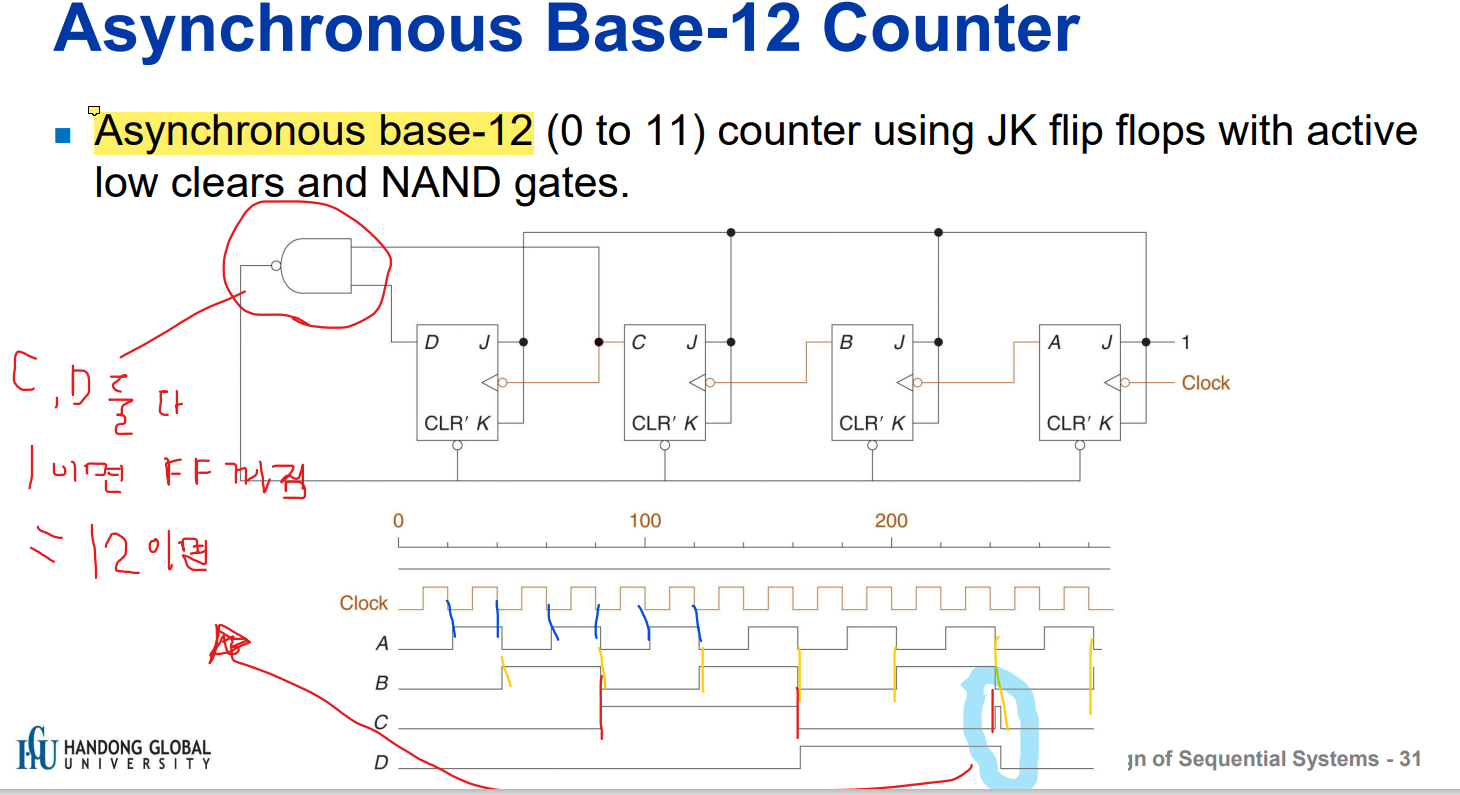

12 base 카운터라는 건, 12 이상은 표현하지 않는다는 뜻이다.

우선 12는 1100이고 그보다 크면 표현하지 않겠다는 건데, 방법이 있다.

11까지만 나오게 하려면 12에서(혹은 더 커지면) 0으로 만들어야 한다.

4비트에서 12가 0이 되게 하려면

@@@@ 4개의 숫자에서

앞에 2개가 11XX이면 12가 넘게 됨.

그때 0으로 만들려면 CLK랑 D와 C의 출력을 NAND로 이어주고, 그걸 CLR로 받아주면 해결!

예제 ) base -60 식을 만들어보셈

60까지 나타내려면 몇 개의 비트가 있어야 하는지 계산 = 비트의 수가 필요한 F/F의 수.

6개가 필요함.

60까지만 나와야 하니까 비트의 구성이 FEDCBA라고 했을 때, 111100면 60이 된다. 그럼 이 뒤로는 뭐가 나오든 0을 내주면 되는 것이니까 F, E, D, C F/F의 결과를 NAND 로 이어주고, NAND의 결과를 6개 F/F의 CLR로 넣어준다.

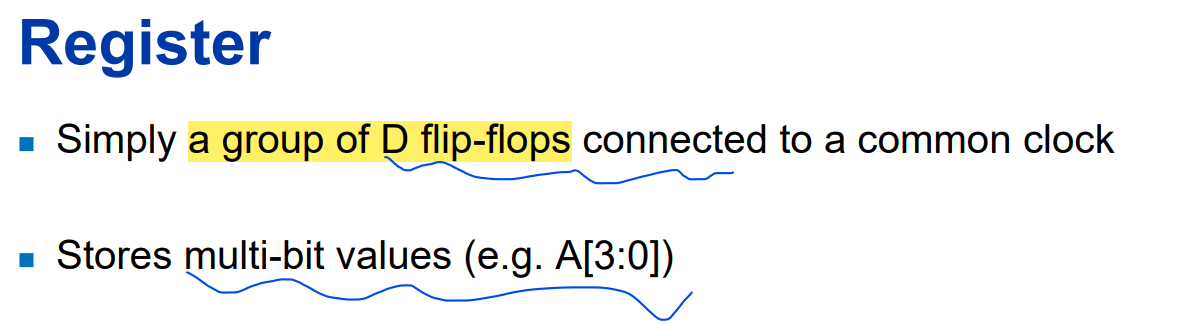

Register

D F/F 여러 개가 하나의 CLK에 묶여있는 형태라고 생각하면 된다.

회로의 양상은 이러하다.

다 같이 하나의 CLR'랑 CLK을 공유함.

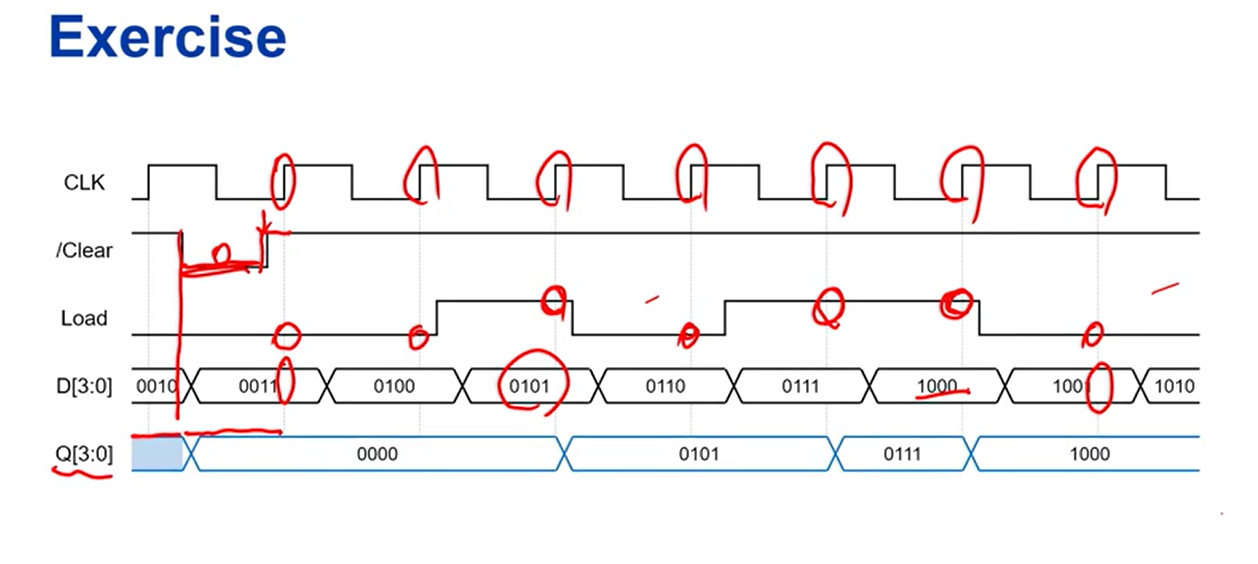

이걸 보면 이해가 더 쉬울 것이다. CLR'가 0으로 켜지면 다음 Edge까지 0000이고, 그게 아니라면, 입력받은 대로 Edge가 돌아간다. 여러 비트가 계산되는 D F/F이라고 생각하면 편할 듯하다.

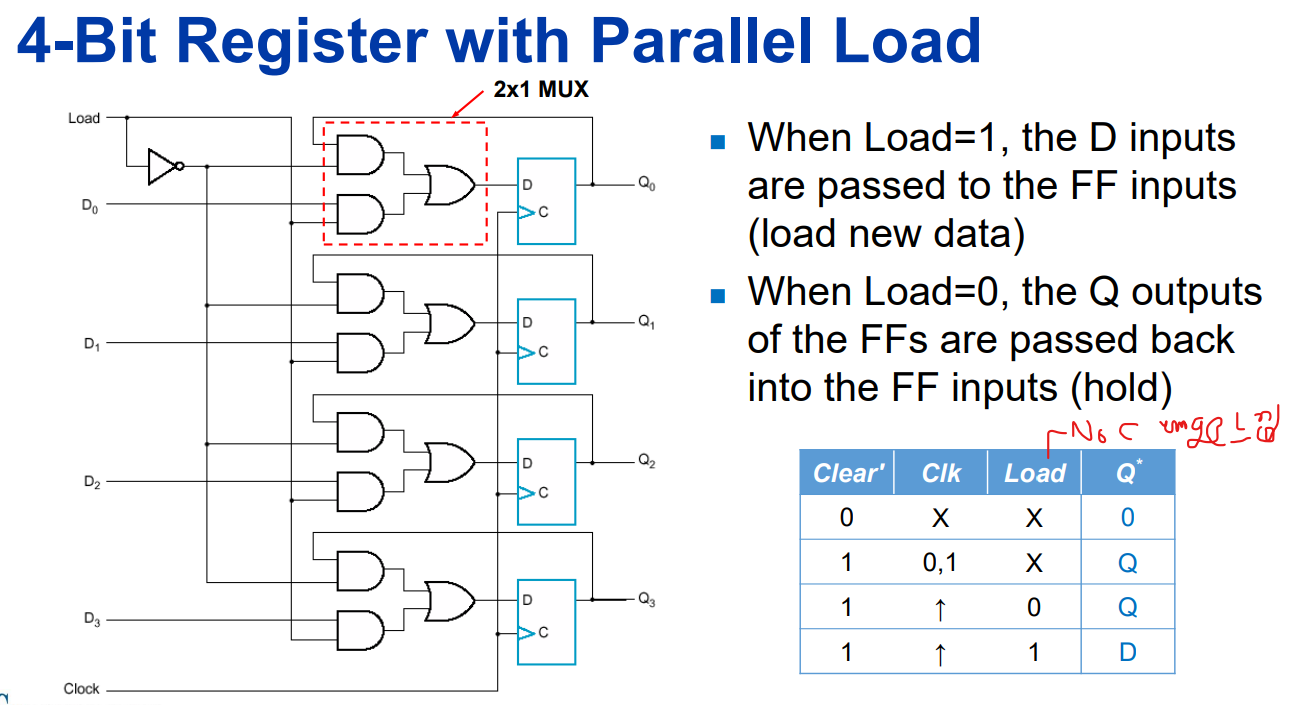

매 사이클에서 Value를 받고 변하는 것 말고, 원하는 사이클에서만 변하는 것도 가능함.

여기에서 Load 개념을 도입할 수 있다. (Enable 써도 됨)

Load랑 D0 , 첫 번째 D F/F쪽을 분석해 보자 (하나만 이해하면 다 이해 가능)

i) Load = 0 이다.

그럼 위 And게이트에만 (Load가 보내는) 1이 들어가고 Q0가 들어온다.

따라서 D에 들어가는 입력은 Q0이므로 이전 상태와 같다. = 새로운 Input을 받지 않는다.

ii) Load = 1 이다.

그럼 아래 And게이트에만 (Load가 보내는) 1이 들어가고 D0이 들어온다.

따라서 D에 들어가는 입력은 D0이므로 새로운 값이 들어오고 결과가 나온다.. = 새로운 Input을 받았다.

Load = 0 는 JK(SR)의 No change의 역할과 같다고 한다.

load가 0이면, F/F은 자신의 이전 상태를 그대로 유지하고 변하지 않는다.

load가 1이면, F/F은 자신이 받은 입력으로 변한다.

--> 받은 데이터(입력)를 load하냐 안 하냐 차이

첫 Edge에서는 load가 계속 안 되어 있어서 그 전 어느 값인지 알 수 없기 때문에

4번째 edge에서는 load도 켜져 있으므로 해당 edge의 입력을 받는다.

CLR는 CLK 신경 안 씀.

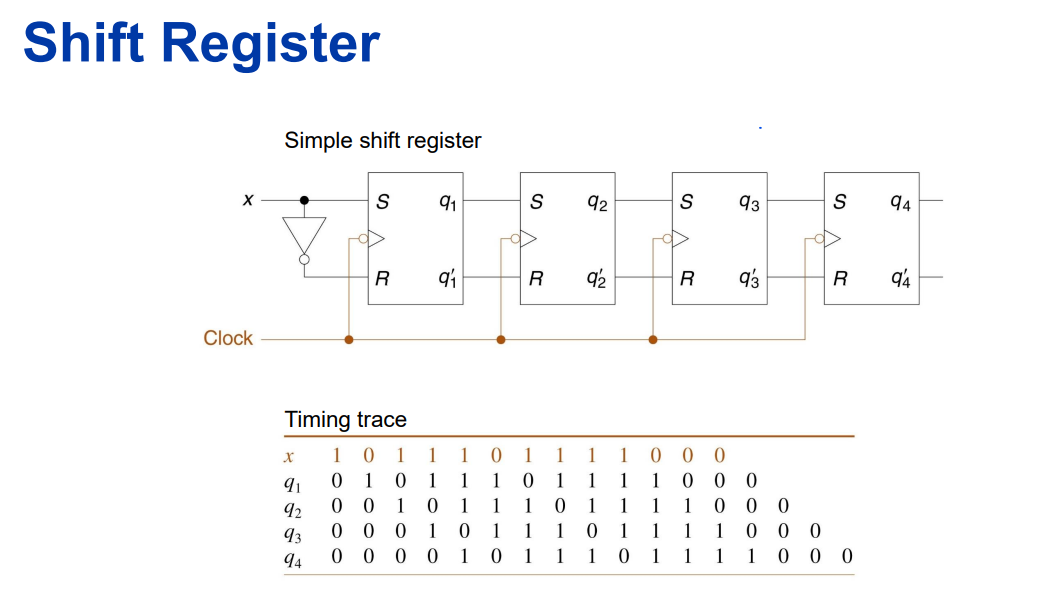

그냥 Sin R이나 L에 들어오는 게 안에 있는 애들 밀면서 들어가는 거

SinR 현재 다음

1 0000 1000 (오른쪽에서 밀면서 들어감)

0 1111 0111

SinL 현재 다음

1 0001 0011 (왼쪽에서 밀면서 들어감)

0 1110 1100

Parallel Load는 그냥 각 한 비트마다 하나의 F/F이 있어서 그거에 맞게 변함

SR F/F으로 구현하는 걸 보자.

X=1일 때, 모든 게 0인 상태에서 1이 들어왔을 때, CLK time에 첫 번째 SR F/F의 결과는 1이 나온다 (S=1, R=0이라서)

그다음 CLK time에는 q1 = 1, q1' = 0 이므로, 그다음 F/F에도 1이 나온다.

X= 0 일 때, 1 0 0 0인데, S=0 , R=1이면 q1 = 0 , q1' =1이 된다.

출처 : 한동대학교 고윤민 교수님 - 논리설계 PPT

'2학년 1학기 > 논리 설계 ( Logic design )' 카테고리의 다른 글

| 논리 설계 25 ( Chapter 8 ) (0) | 2023.06.04 |

|---|---|

| 논리 설계 24 ( Register , Counter ) (1) | 2023.05.30 |

| 논리 설계 22 (0) | 2023.05.26 |

| 논리 설계 21 (0) | 2023.05.21 |

| 논리 설계 20 (The Design of Sequential Systems) (0) | 2023.05.14 |