오래 못 할 짓 하지 않기

논리 설계 25 ( Chapter 8 ) 본문

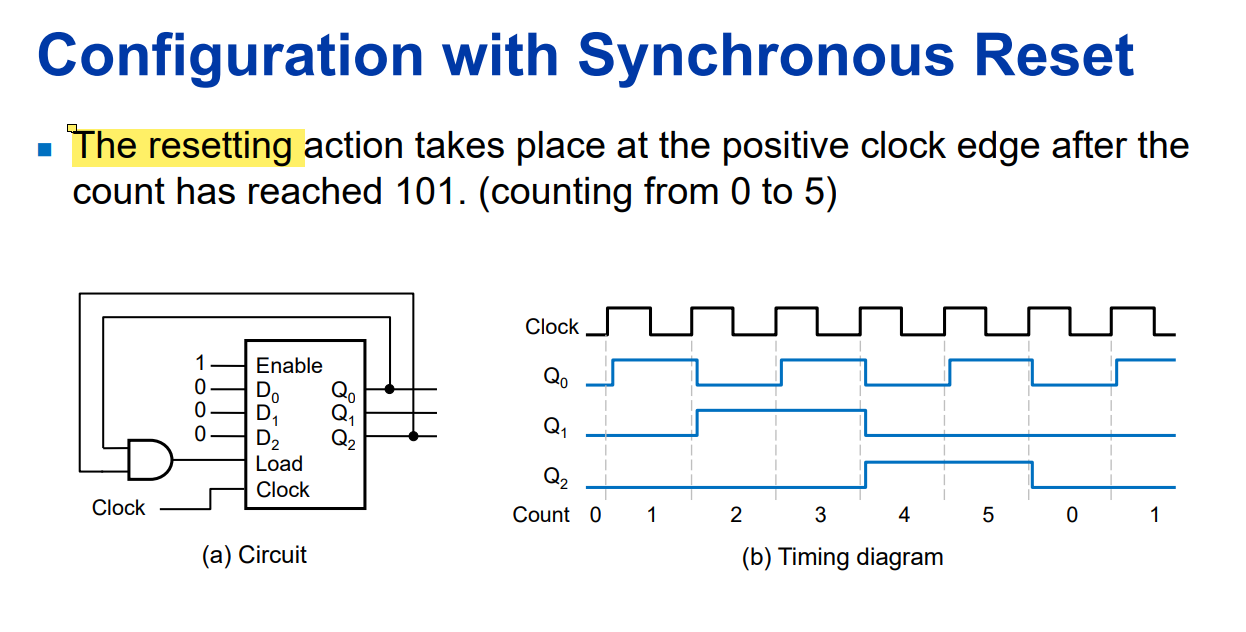

Synchronous & Asynchronous Reset

Reset 시키는 법은 2가지가 있다.

Load로 0을 만들거나 CLR로 0을 만들거나

Synchronous 에서는 Load를 사용하여 원하는 숫자까지 나왔을 때 다시 0으로 CLR 시켜줄 수 있다.

왼쪽)

위 사진\과 같은 경우에는 0000 (0) ~ 1001 (9) 까지 나오게 하는 거면,

1001 이 나오면 AND에 1 1 이 들어가서 LOAD 가 1이 되고,

그 counter에는 CLR가 켜져있고 input이 0이 들어오고 있기 때문에

1001가 되면 그 다음 상태는 0000이 된다.

0 ~ 5까지 나오게 하는 Synchronous reset 이다.

Count 가 5일 때, 5 상태가 되고, 그 다음 상태는 000이 된다.

오른쪽 경우를 보자.

Asynchronous 에서는 CLR를 사용하여 원하는 숫자까지 나왔을 때 다시 0으로 CLR 시켜줄 수 있다.

위 사진도 마찬가지로 0000 (0) ~ 1001 (9) 까지 나오게 한다.

하지만 1001일 때 CLR를 하면 9도 출력이 되지 않으므로

1010 (10) 이 감지되는 순간 reset이 되도록 바꾼다.

위 사진은 0 ~ 4까지만 나오게 하는 회로다.

count가 0 ~ 4 일땐 잘 있다가. 5(의도하지 않은 숫자) 가 나오면 (잠깐이나마 나타나긴 함)

바로 CLR가 작동한다.

Synchronous reset 과 asynchronous reset의 가장 큰 차이는

전자는 원하는 숫자만 나오고

후자는 원하는 숫자 마지막의 다음 숫자가 나오는 순간 reset이다.

BCD Counter

4비트가 BCD 한 세트라고 볼 수 있다.

한 세트에서는 9까지만 나타내고, 그 다음 비트는 그 다음 자릿수를 나타낸다

ex) 54

= 0101(5) 0100 (4)

회로를 분석해보면, 9까지만 나타내기 떄문에

9가 되었을 때 And 게이트는 다음 BCD 세트 Enable에 1을 준다.

그렇게 한 번 켜져서 0001 이 된 다음 BCD 세트는 다시 꺼져서 숫자는 그대로 유지된다.

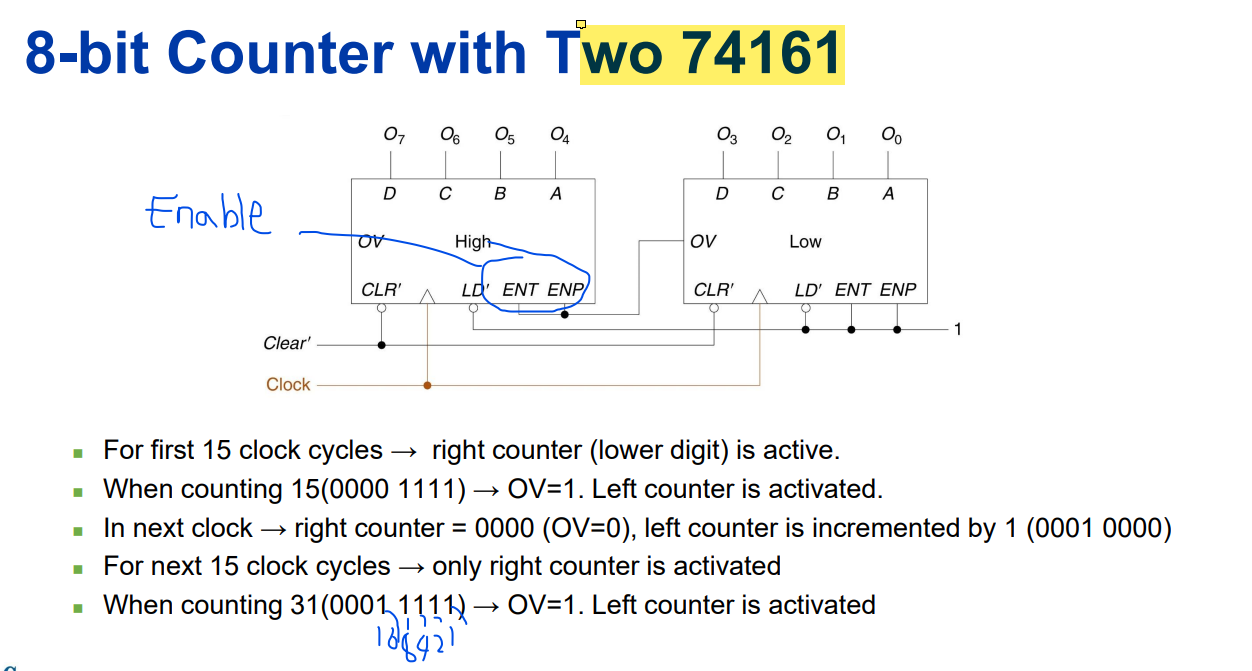

설명

- 첫 15 CLK 사이클동안은 오른쪽(만) Active 상태이다.

- 그리고 LOW 쪽이 15 (1111이 되면) OV=1이 되면서,

왼쪽 카운터 EN@ 에 1이 전달되고, 왼쪽도 1개가 켜진다. ( 0001 0000 = 16 ) - 0001 0000 상태면 OV 은 다시 0이 되고, 왼쪽 카운터 EN@ 들도 꺼지면서, 다시 왼쪽만 증가함.

Static Clear

0~ 119까지만 출력하려면 = 120이 되는 순간에 0으로 만든다.

120을 만드는 조합들을 NAND에 넣고, CLR에 넣어준다.

1) 0이 되게 하려는 해당 숫자를 2진법으로 구한다.

2) 몇 번째 숫자가 0이고 1인지 구한다.

3) 그 순서에 해당하는 Output 들을 Nand로 묶는다.

4) CLR에 넣는다.

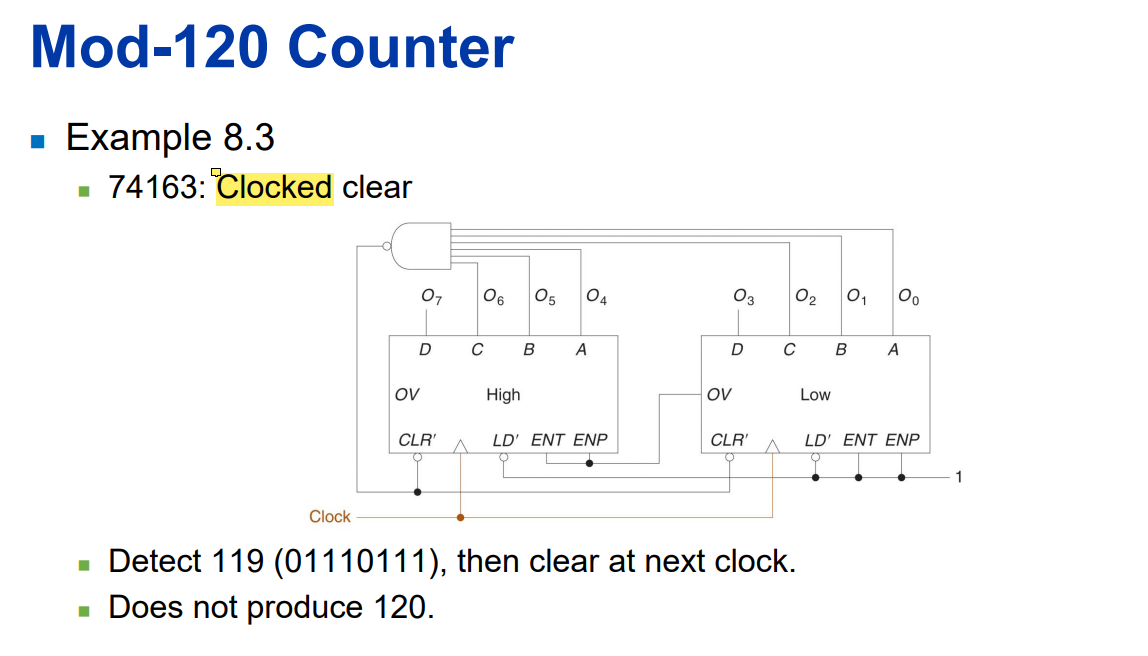

Clocked clear

0~ 119까지만 출력하려면 = 119 다음 CLK에 CLR되게 한다.

119를 만드는 조합들을 NAND에 넣고, CLR에 넣어준다

1) 몇 번째 숫자까지만 나오게 할지 정한다. -- >N번째

2) N을 2진수로 했을 때, 몇 번째 숫자가 0이고 1인지 구한다.

3) 그 순서에 해당하는 Output 들을 Nand로 묶는다.

4) CLR에 넣는다.

출처 : 한동대학교 고윤민교수님 - 논리설계 PPT

'2학년 1학기 > 논리 설계 ( Logic design )' 카테고리의 다른 글

| 논리 설계 26 (Simplification of Sequential Circuits) (0) | 2023.06.06 |

|---|---|

| 논리 설계 24 ( Register , Counter ) (0) | 2023.05.30 |

| 논리 설계 23 (Asynchronous Counter , Register) (0) | 2023.05.27 |

| 논리 설계 22 (0) | 2023.05.26 |

| 논리 설계 21 (0) | 2023.05.21 |