오래 못 할 짓 하지 않기

[ 컴퓨터 구조 ] 3. Datapath (2) - Simple Datapath 본문

Register file : 32개의 register가 모여있는 모듈 정도로 생각하면 됨

분석 :

- [ 명령어를 담고 있는 메모리 ]와 [ 데이터를 담고 있는 메모리 ] 가 나누어져 있다.

- 연산을 담당하는 ALU가 있다. (그냥 연산하는 회로담당이라 생각하면 됨)

- Register를 모아놓은 Register File이 있다.

- 명령어의 주소를 담고있는 PC(Program Counter)가 있다.

메모리 2개가 나누어진 이유 : 1CLK cycle에 모든 걸 다 하려고 하기 때문에 Cycle마다 명령어를 읽기 위해

- 작동 방식

1. PC에서 나온 값이, Instruction memory의 address로 들어감

2. 그 address에 있는 Instruction memory(32bit)를 분석함. ( 앞 6비트는 OP code / R,I,J 중 무슨 타입인지... )

3. Register #1,2 (Rs,Rt)에 해당하는 값들은 각각 ALU로 들어가고, ALU에서 주어진 연산 작업을 한다.

4. 연산된 결과가 Register file 의 Data in 으로 들어가고, 이것을 어디에 쓸지는 Rd 가 정한다.

PC 에서 나온 거 → Instruction memory → Register file → ALU → ALU의 결과가 Rd 필드에 있는 주소로 write → PC+4

(+ 메모리에 대한 읽기, 쓰기를 하기 위해서는 주소 계산을 해야하는데, 그때는 Rs + imm16를 해야 한다.)

(+ Addi 인 경우에는 Rd = Rt로 바꾼다. )

정밀 분석

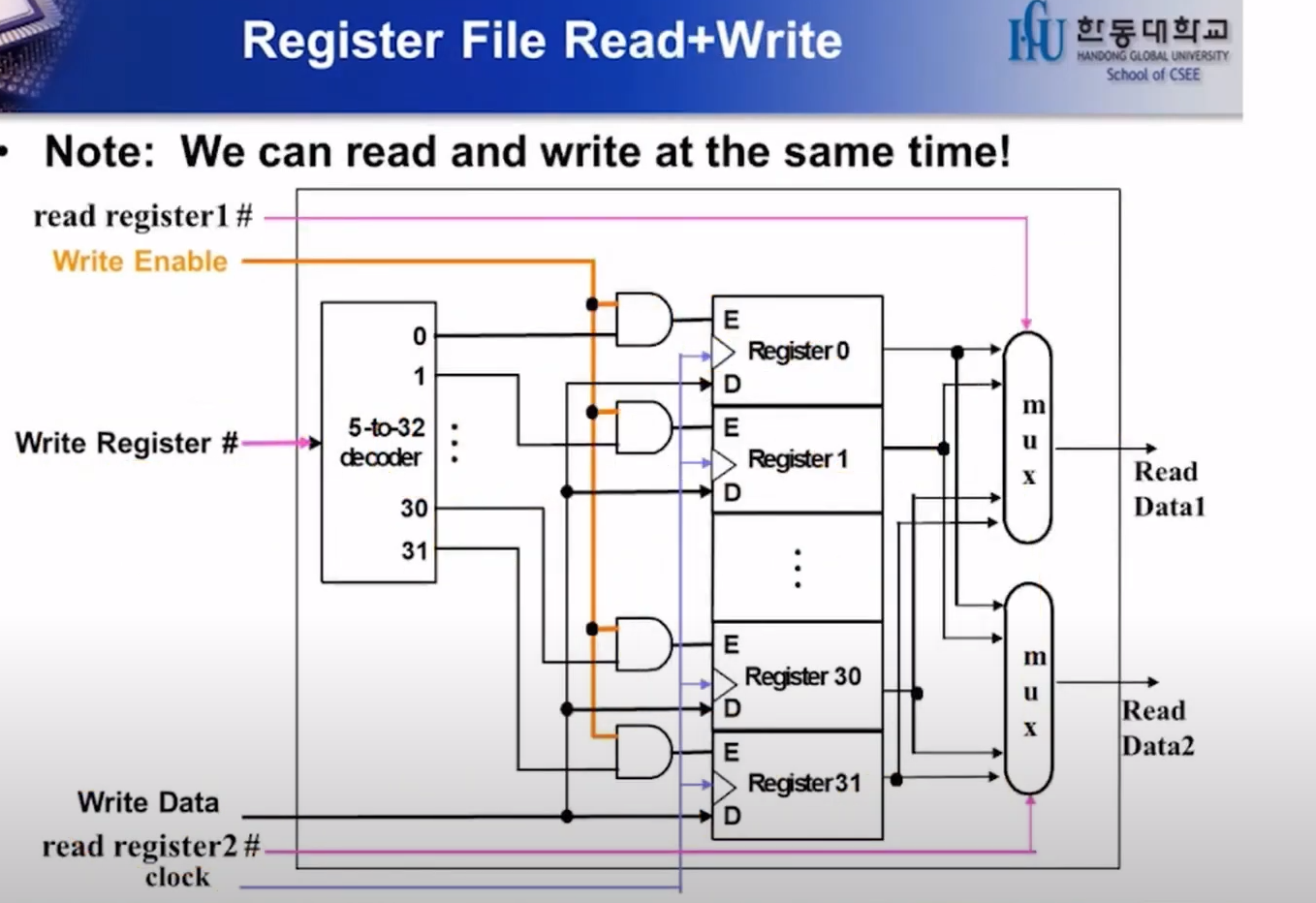

Register File을 자세히 볼 거다.

- 32개의 Register가 있고, 각각의 Register 안에 32비트가 있다.

- Register (read/write) = 5비트 / Data = 32비트

- 어떤 데이터를 쓸 건지는 Write data에서 정함.

- Read 정밀 분석 (Register 1,2)

- 32개의 Register (0~31번째) 가 있다.

- 이 Register의 값이 MUX에 들어간다 ( 32:1 MUX )

- 그중에 하나의 값이 선택되어 Data로 read 된다.

- Write 정밀 분석

- 우선 각 Register들에게 Data Input과 Enable input이 있다.

- Data Input 은 왼쪽 아래에 있는 Write Data에서 들어오는 정보가 된다.

- Enable input은 Write Register에서 Decoder를 이용하여 하나의 출력에만 1을 주어

Enable이 켜지게 하는 원리로 작동한다. - 0번 Register는 상수임.

Read는 CLK에 상관 X

Write는 상관 O

ALU 신호 종류 4개

- 앞에 두 비트는 A-invert , B-invert → Operand

뒤에 두 비트는 어떤 연산을 할지 → Operator

(+ 빼기 할 때는 A+ B' 이런 식으로 보수로 함.)

- 00 = and / 01 = or / 10 = add / 11 = 비교기

우리가 사용하는 구성요소들

1. Register FIle

2. Instruction Memory (Read Only Memory = 읽기만 함) + Data memory

3. ALU

4. Program Counter (PC)

5. Adder

6. Sign-extention (16bit를 복사하고, 부족한 나머지 bit는 입력으로 들어온 sign bit를 복사하여 원하는 bit수로 맞춰줌)

어떤 걸 할 때 뭐가 필요한지 알아야 함.

ex) Instruction Fetch 할 때 → Instruction Memory + Program Counter + Adder

ALU 에 대한 정보 :

ALU가 받는 입력에 대한 정보들로는

[ 피연산자 ] 와 [ 연산(명령) ]이 있다.

피연산자들은 레지스터에서 내용을 가져오고,

연산 명령들은 제어장치(PC)에서 가져온다.

그 결과는 rd에 저장.

레지스터에 대한 정보 :

1. 프로그램 카운터 - 메모리에서 가져올 명령어의 주소

2. 명령어 레지스터 - 해석할 명렁어 ( 방금 메모리에서 읽어 들인 명령어 ) < 제어 장치가 해석

3. 메모리 주소 레지스터 - 메모리의 주소를 저장

4. 메모리 버퍼 레지스터 - 메모리와 주고받을 값 ( 데이터와 명령어 )

'2학년 2학기 > 컴퓨터 구조' 카테고리의 다른 글

| [ 컴퓨터 구조 ] 6. (Multiple Cycle) Multiple Clock Cycle (0) | 2023.07.04 |

|---|---|

| [ 컴퓨터 구조 ] 5. Single Cycle 제어부 (0) | 2023.07.04 |

| [ 컴퓨터 구조 ] 4. Datapath (3) - Instruction Datapath (0) | 2023.06.30 |

| [ 컴퓨터 구조 ] 2. Datapath (1) (0) | 2023.06.28 |

| [ 컴퓨터 구조 ] 1. RISC / MIPS (0) | 2023.06.27 |