오래 못 할 짓 하지 않기

[ 컴퓨터 구조 ] 15. (Hazard) Data Forwarding logic 본문

▣ Data Fowarding 이 필요할 때

: Data hazard가 발생했을 때 = Register Data들끼리 Dependency 가 있을 때임

→ Register file에 Write는 CLK의 앞부분 , Read는 뒷부분에서 일어나서 같은 Stage에 겹치더라도 ㄱㅊㄱㅊ

때문에 Dependecy가 있는 파일을 쓰고, 그 다음 명령어에서 읽는 것이 [ 같은 Stage일 때 ] 는 Hazard가 발생 X

하지만, 그 이상일 때는 어떻게 할 것인가?

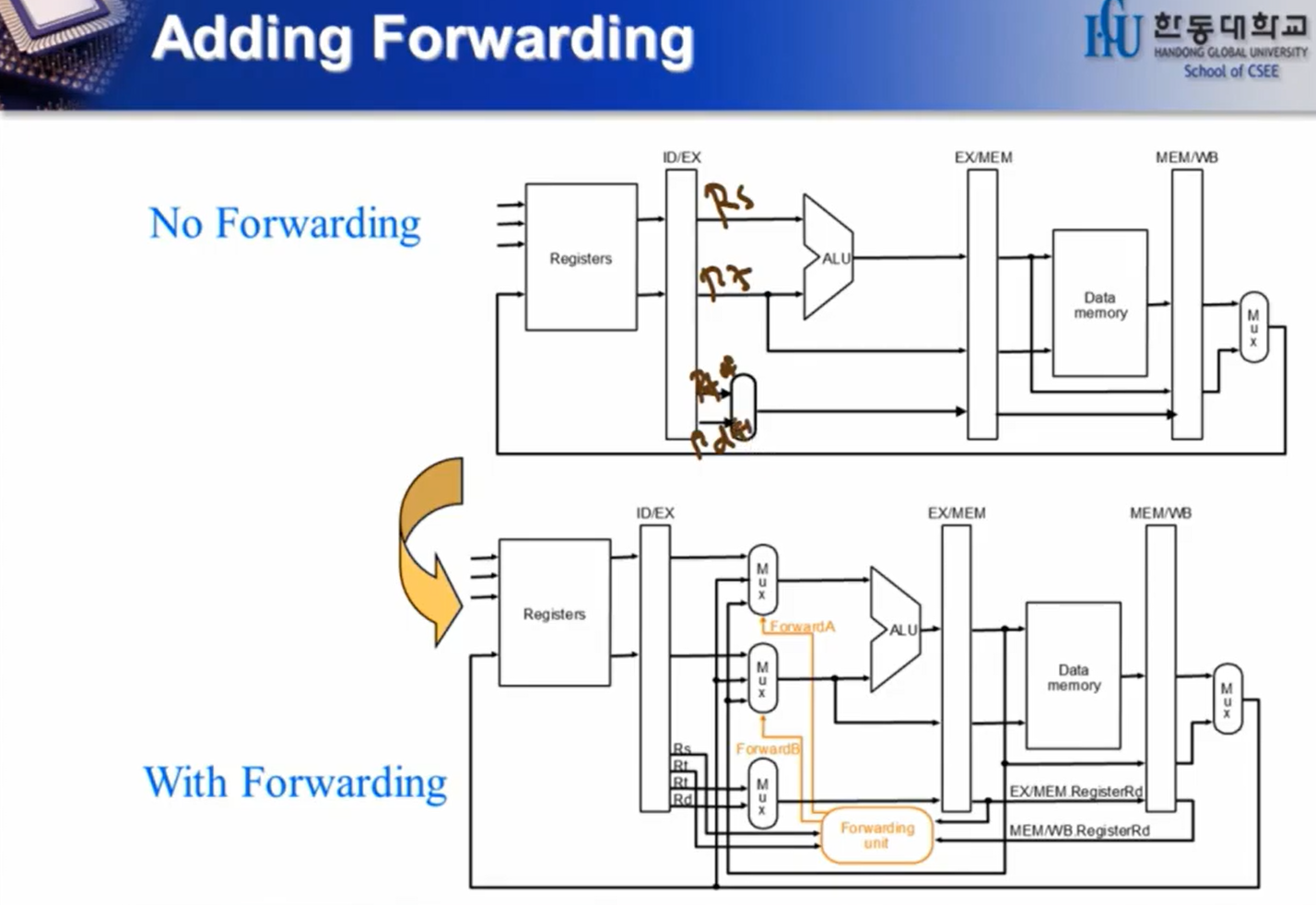

☞ Data Forwarding

R-Type 연산의 결과는 5번째 CLK에서 " 저장 " 되지만

저장이 아닌 연산이 실행되고 끝나는 것은 3번째 CLK에서 끝난다.

▣ 따라서, 이 정보를 가져와서 Dependency로 인한 hazard를 없애기 위해서는

EX Stage에서 나온 결과를 다시 뒤에 Dependecy 명령어의 EX 입력값으로 넣어주면 된다.

Forwarding을 할 경우에는 3:1 MUX를 설치한다.

▣ ALU에서의 연산 결과로 나온 주소(먼저 실행한 명령어의 결과) 를

다시 ALU에 넣는다. ( Dependency 한 명령어의 EX단으로 취급)

RS로 넣을지 RT로 넣을지 어디로 넣을지에 대한 MUX

또는 2 CLK 차이나는 명령어인 경우에는 WB단에서 가져와야 하기 때문에 그거에 대한 MUX

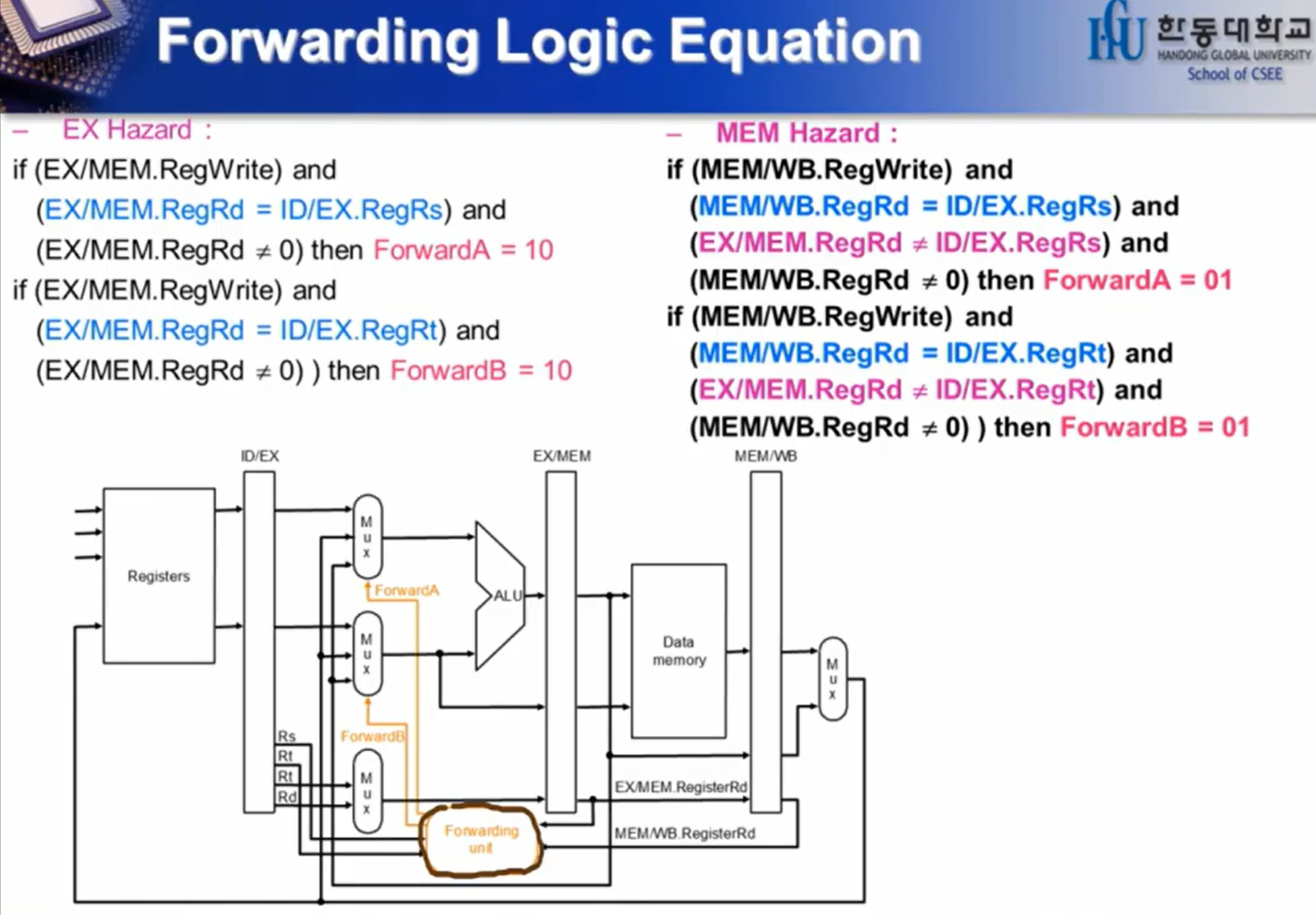

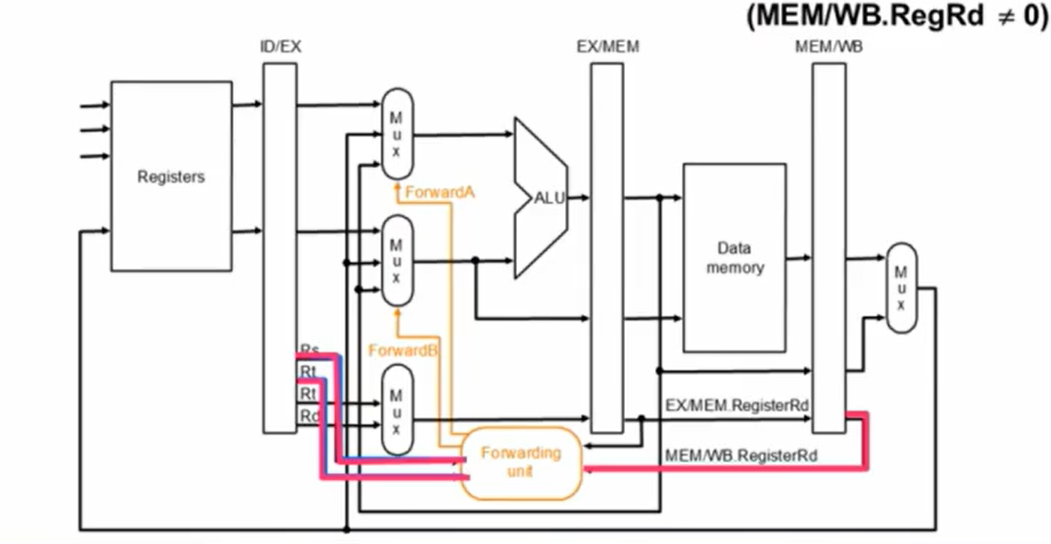

Forwarding Unit Logic

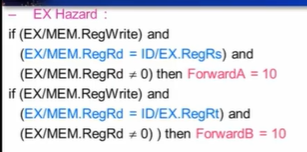

(왼쪽 위) EX Hazard 부분 : EX단과 MEM 단에서 발생하는 Hazard

이 부분을 담당하는 게 Forward A이다. ( 00 : Register file에서 읽어옴 / 01 : WB 에서 읽어옴 / 10 : MEM에서 읽어옴 )

▣ EX Hazard - If 해석 ( 먼저 실행되었고, EX/MEM에 있는 명령어 A , 뒤에 실행된 ID/EX에 있는 (Dependency) 명령어 B)

- [ A가 Register Write 를 하는 명령어인가? ]

- and [ B가 A의 Dependecy인가? ] ← (A의 Rd = B의 Rs or Rt 인가? )

- and [ A의 Rd가 0이 아니라면 ](이게 뭔 뜻인지 잘 모르겠음) → 그렇다면 10, MEM에서 읽어와라.

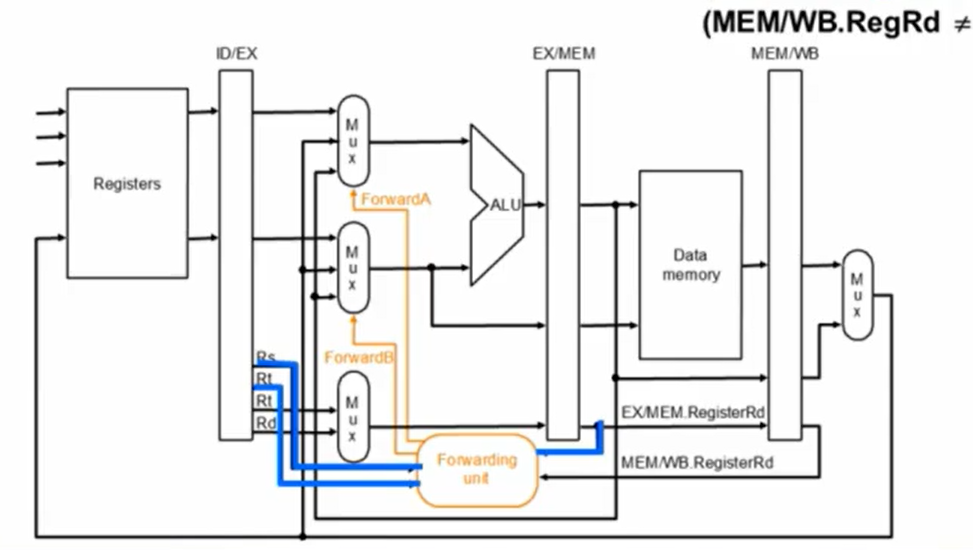

파란색 선으로 (오른쪽 → 왼쪽) 으로 데이터가 이동함.

▣ MEM Hazard - If 해석 ( MEM Hazard는 2단계 떨어진 명령어들끼리 Data Hazard가 일어날 때를 해결하기 위함)

( 먼저 실행되었고, MEM/WB에 있는 명령어 A

그다음 실행된 EX/MEM에 있는 명령어 B

그 뒤에 실행된 ID/EX에 있는 명령어 C

- [ A가 Register Write를 하는 명령어 ]

- and [ C가 A의 Dependency이어야 한다. ] ← (A의 Rd = B의 Rs or Rt 이어야 한다. )

- and [ C가 B의 Dependency는 아니어야 한다 ] ← (B의 Rd != B의 Rs or Rt 이어야 한다. )

- and [ Rd = 0이 아니라면 ](이게 뭔 뜻인지 잘 모르겠음) → 그렇다면 10, MEM에서 읽어와라.

16분부터는 아래

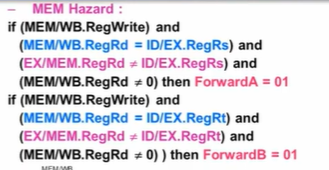

(예제)

▣ 2번 Register에 sub결과가 들어가야 그 아래 and와 or 연산에서 결괏값을 사용할 수 있기 때문에 Dependency.

▣ 4번 Register에 And 결과가 들어가야 그 아래 or와 add에서 사용가능.

▣ 4번 Register에 or 결과가 들어가야 그 아래 add에서 사용가능.

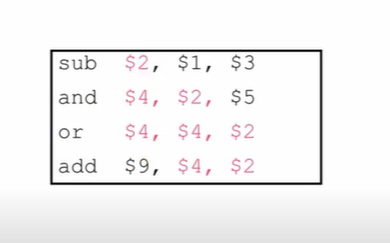

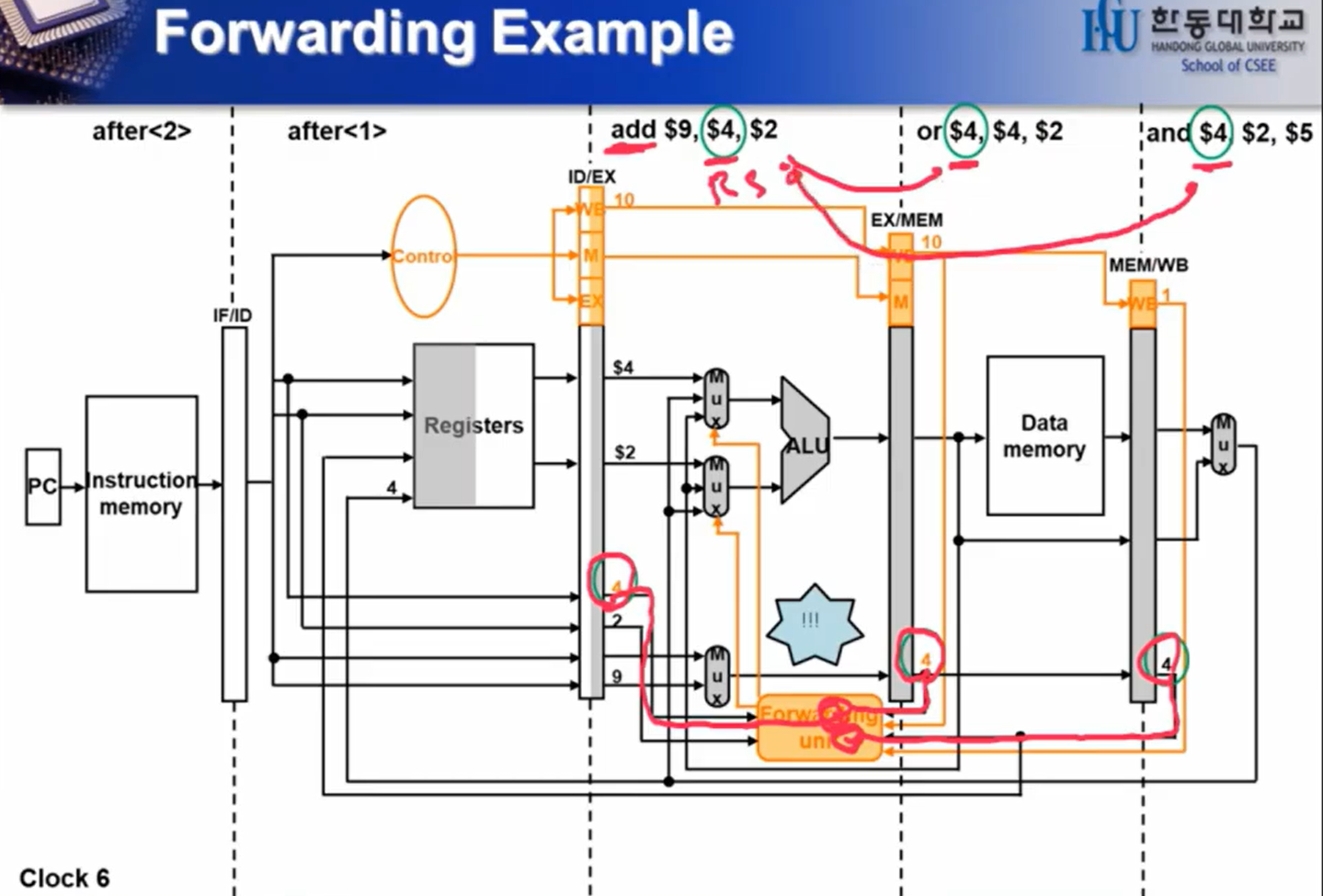

위 사진에서 보았을 때,

EX Hazard - If 해석한 대로

앞 명령어의 Rd = 그 뒤 명령어 Rs or Rt인가를 보고 맞기 때문에

forwarding unit에서 그걸 판단하고 그 주소를 보내준다.

and 명령어의 목적지이자 or명령어의 목적지이기도 하다.

이 명령어를 쓸 때는 add 연산을 할 때인데, 가장 최신의 명령어 (or) 의 목적지를 가져온다.

(당연하긴 함 or는 and연산까지 다 마친 값을 갖고 있고, and는 or연산 결과의 값이 없기 때문에)

지금까지 R-type 명령어들로 인한 Data Hazard 를 다루는 방법을 배웠다.

다음은 LW로 인해 발생하는 Data Hazard를 다루어보자

Data Hazard By [ LW ]

LW 의 결과를 2번 Register에 저장하는데,

그걸 Write 되는 건 5번째 CLK일 때고 , 그 Data의 값이 나오는 건 4번째 CLK일 때이다.

값이 나오는 건 MEM고, 이 값들이 필요한 곳은 ALU가 있는 EX stage이다.

하지만, 앞 명령어가 MEM을 실행하고 있을 때, 그다음 명령어는 이미 EX이기 때문에

다음 명령어는 MEM의 값을 받을 수 없고, LW 명령어와 (빨라야) 2 CLK 차이나는 명령어부터는

Forwarding으로 그 값을 받을 수 있다.

그럼 그냥 받으려면 어떻게 해야 하나?

1 CLK을 지연시키면 된다. Stalling = NOP를 삽입하여 가장 빠른 다음 명령어가 2 CLK차이가 나게 만드는 것이다 이말

[설계]

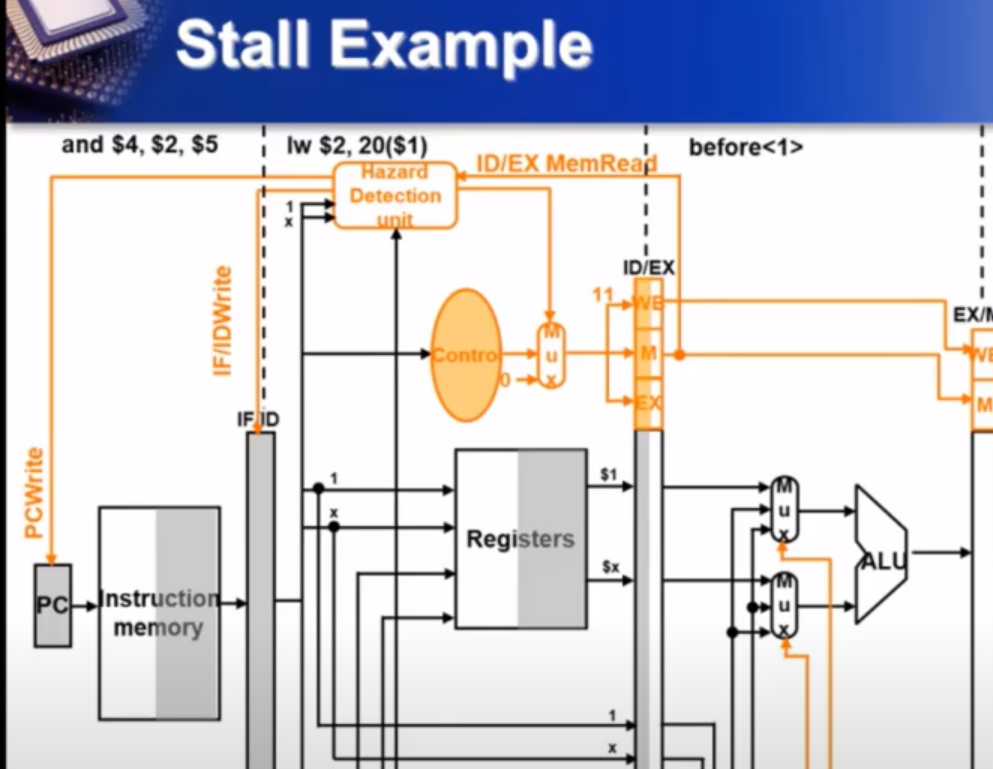

원래 만들어져 있는 Forwarding unit에 새로운 Hazard Detection Unit을 만든다.

또 Stall (=NOP) 효과를 내기 위해 Control 신호들을 모두 0으로 바꿀 수 있어야 한다.

If 조건문 분석 / 먼저 실행된 LW명령어 A, 그 뒤에 실행되는 명령어 B

( A가 Memory에서 뭘 읽는 명령어 * (( A 의 Rt = B의 Rs or Rt)) 이다? → Stall (NOP)

5개 중에 1개의 stage만 쉬게 하는 거다.

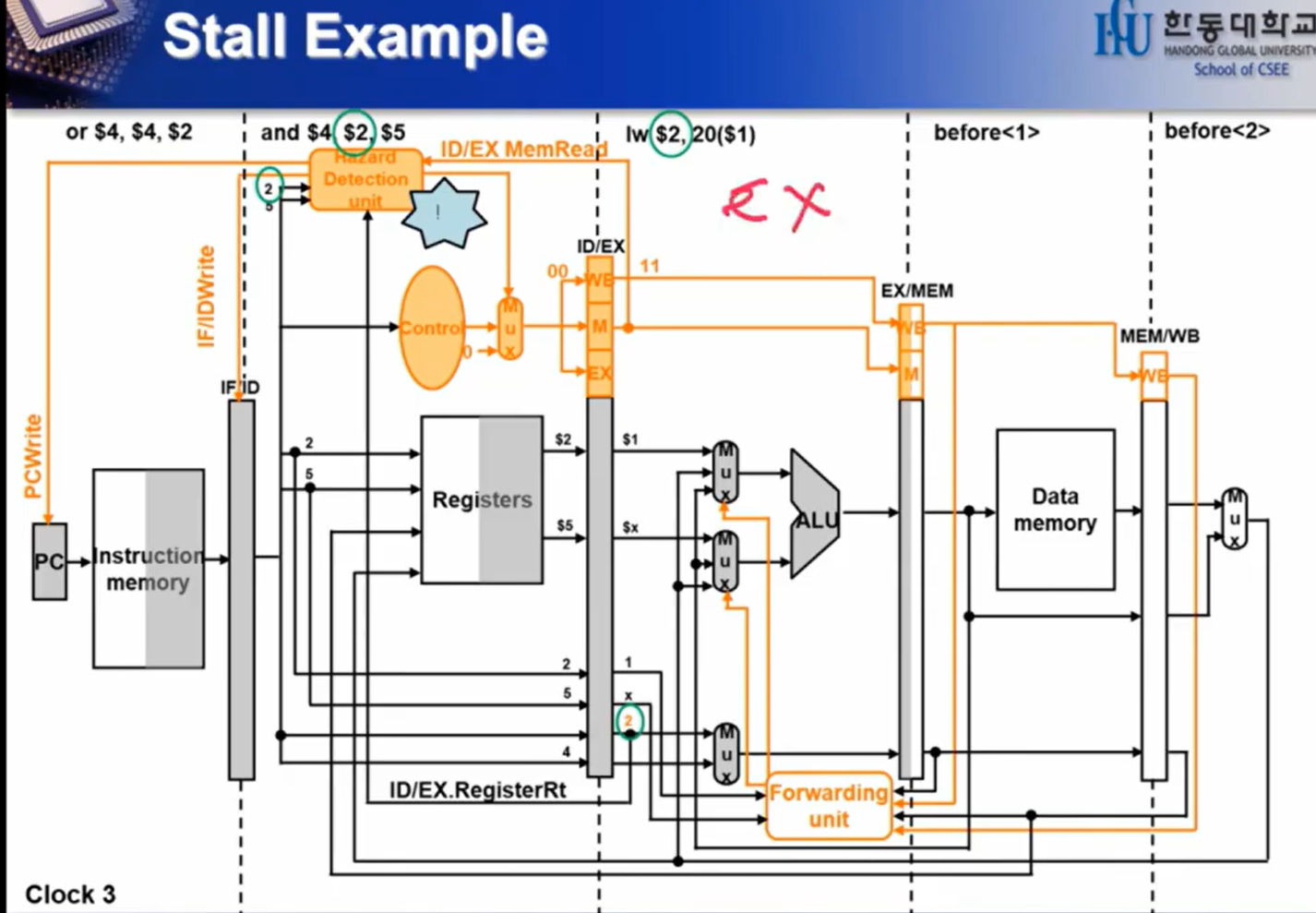

(예시)

이 두 명령어 간에 Dependency가 있고 한 칸 차이.

두 명령어 사이에 NOP를 넣어야 한다.

이걸 인지하고, 동작을 수행할 수 있는 가장 빠른 시점은 LW= EX stage, And = ID일 때이다.

(아래 설명 맞는지 모르니까 나중에 공부하고 수정하셈)

If 분석한 거 써먹을 때임.

▣ LW니까 Memory read를 함. → ID/EX register에서 1이 나오고, Hazard detection unit이 켜짐

▣ EX단에 들어온 명령어의 Rt값이 2 , ID 단에 들어온 명령어의 Rt값이 2 → Hazard detection unit이 켜짐

= Hazard 발생. → Control 옆에 있는 MUX 를 통해서 그 뒤에 들어갈 값들 다 꺼버림 (Enable = 0)

▣ and는 그다음 칸으로 넘어가려면 그 register가 enable 되어 있어야 하는데 아니라 못 넘어가고 EX단은 한 CLK 논다.

Bubble 덕에 2 CLK 차이가 나면서, Forwarding unit을 통해서 Lw의 값($2)을 and에서 사용할 수 있다.

출처 : 한동대 SW중심대학

'2학년 2학기 > 컴퓨터 구조' 카테고리의 다른 글

| 컴퓨터 구조 1 (0) | 2023.09.01 |

|---|---|

| [ 컴퓨터 구조 ] 16. (Hazard) Flushing logic (0) | 2023.07.11 |

| [ 컴퓨터 구조 ] 14. Control Hazard solutions (0) | 2023.07.09 |

| [ 컴퓨터 구조 ] 13. Data Hazard (0) | 2023.07.07 |

| [ 컴퓨터 구조 ] 12. Pipeline 제어부 (Control) (0) | 2023.07.07 |