오래 못 할 짓 하지 않기

[ 컴퓨터 구조 ] 17. Datapath - Pipeline with Control signals 본문

Single CLK cycle - Datapath

한 stage에서 나온 결과값을 다음 stage에 전달해주기 위해서는 사이에 Register가 필요하다

주로 이런 그림으로 표현할 때 왼쪽을 색칠하면 Reg Write / 오른쪽을 색칠하면 Reg Read로 이해하면 된다.

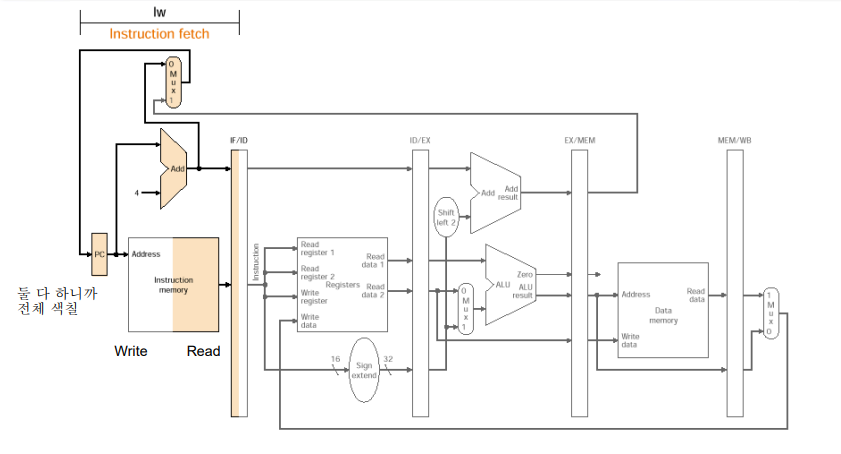

Pipeline에서 LW를 실행했을 때 Datapath를 분석

1. Inst fetch

- PC값을 읽고, ADDER와 MUX를 통해서 PC+4값을 새로 write한다.

- Inst 메모리에서 명령어를 읽고, 해당 명령어를 다음 단에 넘겨주기 위해 Stage 사이에 있는 Register에 write한다.

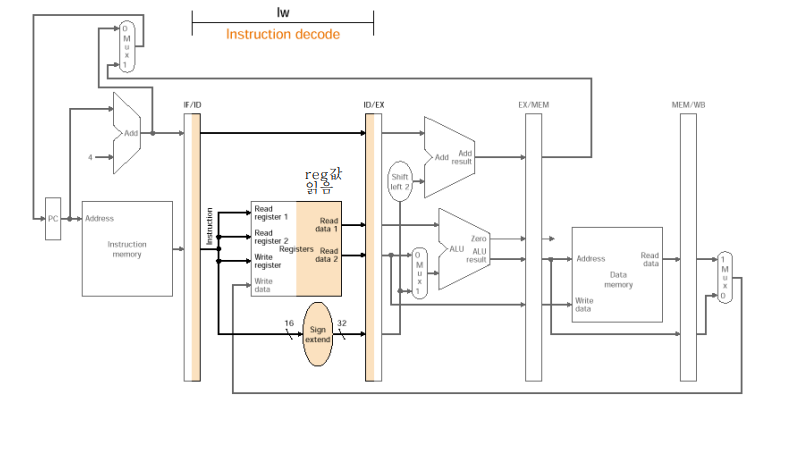

2. Inst decode

- IF에서 넘어온 2개의 Register 값을 읽고, Extension한 비트를 계산하여 target address를 미리 계산하여

EX 단으로 넘어갈 수 있도록 Stage Register에 write

- Branch 할 경우를 생각하여 위에서 PC값도 계속 가져간다.

3. Execution

- Sign Extent한 값과 Read data1 한 값을 더하여 그 주소를 MEM stage로 넘겨준다.

- Branch할까봐 위에서 아직도 PC+4값을 갖고있지만 사용하지 않는다.

4. Mem access

- 앞에서 받은 주소값으로 Data Memory에서 원하는 값을 Read한다.

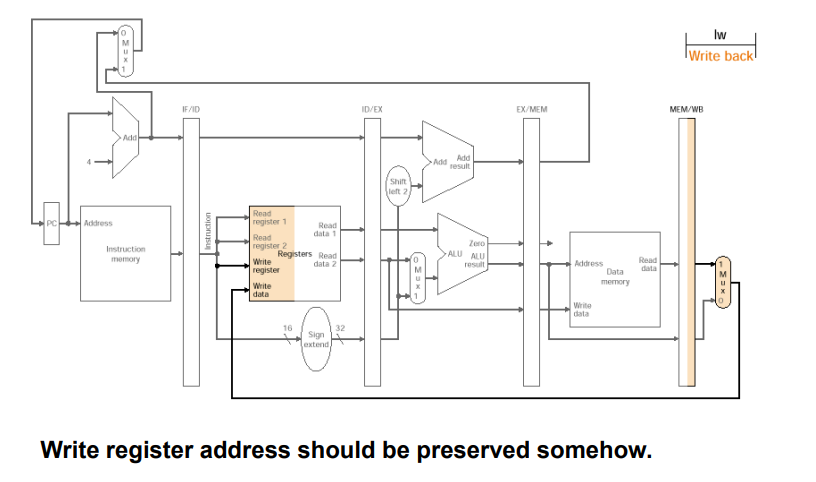

5. Write back

- Write 할 register 주소에 Data Mem에서 가져온 값을 적는다.

하지만!

LW만 진행되고 있는 경우엔 문제가 없었지만 그 뒤에 따라오는 Inst가 있었다면 어떨까?

우리가 Write back하려고 Reg File로 돌아갔을 때, 해당 stage에서 ADD 명령어같이 실행되고 있다면

우리가 설정한 LW에서의 Write Register와 ADD의 rd를 어떻게 처리해야할까?

수정본 ( 주황색 줄을 추가한다 )

Write reg주소를 끝날 때까지 같이 넘겨주고, 마지막에 얘가 필요할 때만 연결한다.

그럼 따라오는 명령어들도 이 부분을 차지하지 않기 때문에 겹칠 일이 없다.

나올 수 있는 질문

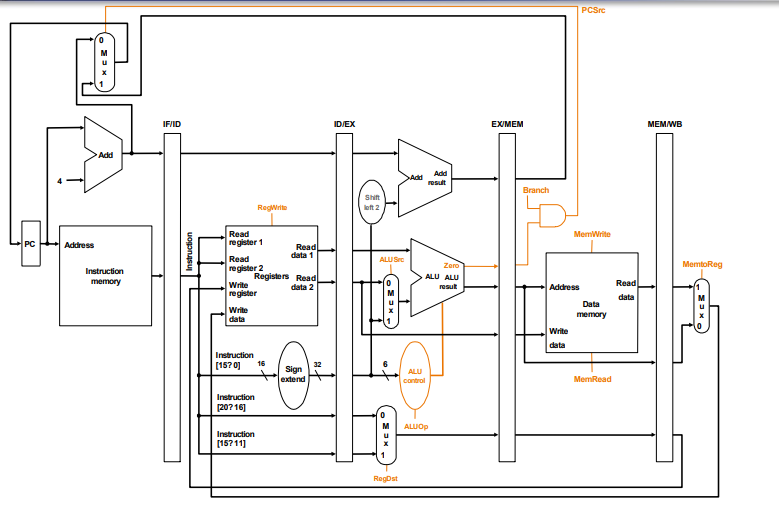

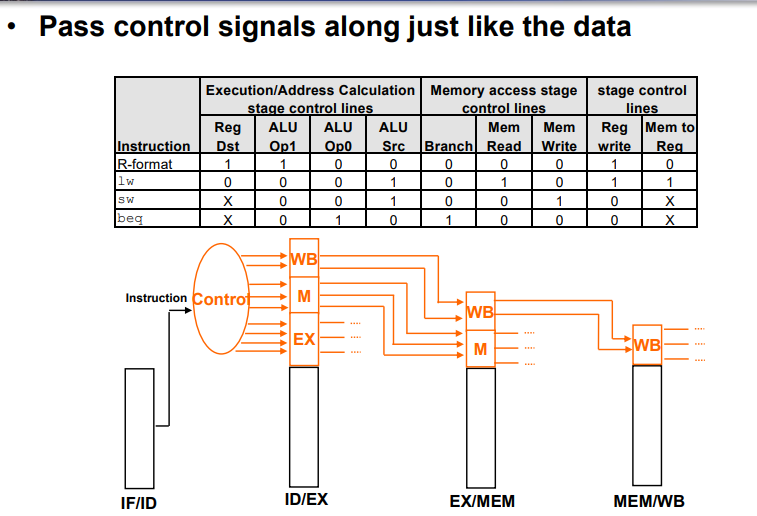

Pipeline Control

각 Stages ( steps ) 에서 Control 되어야 하는 것

- IF : 딱히 control 할 거 없음

- ID : 딱히 control 할 거 없음

- EX : 명령어에 따라 RegDst , ALUOp , ALUSrc

- MEM : 명령어에 따라 Branch, MemRead, MemWrite

- WB : 명령어에 따라 MemtoReg , RegWrite

그렇다면 어떻게 Control sign을 만들어내서 제어를 할까?

→ 택배물류를 생각해보자. 중앙에서 한 사람이 " 그 택배 어디로 보내, 저 택배 어디로 보내. " 가 아니라

그냥 물건에 송장이 붙어있고 그거대로 물류 센터에서 송장번호에 따라 통제가 된다.

Pipeline 도 마찬가지다. Instruction을 보고 어떤 걸 보낼지 정한다.

ID stage에서 모든 Control 신호들을 Pipeline register에 생성한다.

설명 :

- ID stage에서 그 뒤에 쓰일 제어 신호들을 한 번에 모두 생성한다.

- 그다음 EX단에서 사용되는 신호들을 거기에서 쓰이고 종료.

- 또 그 다음 Memory단에서 사용되는 신호들도...

- WB...

++ 제어신호들은 파이프라인 register에 같이 붙음.

Control 신호까지 있는 Pipeline은 아래와 같다.

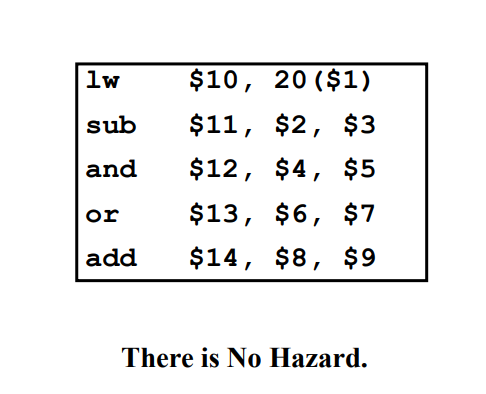

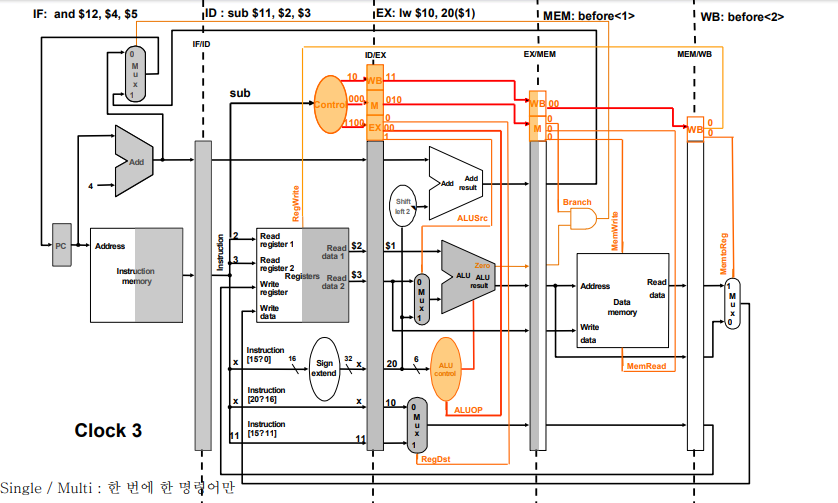

예)

이 명령어를 Pipeline에서 실행해보자

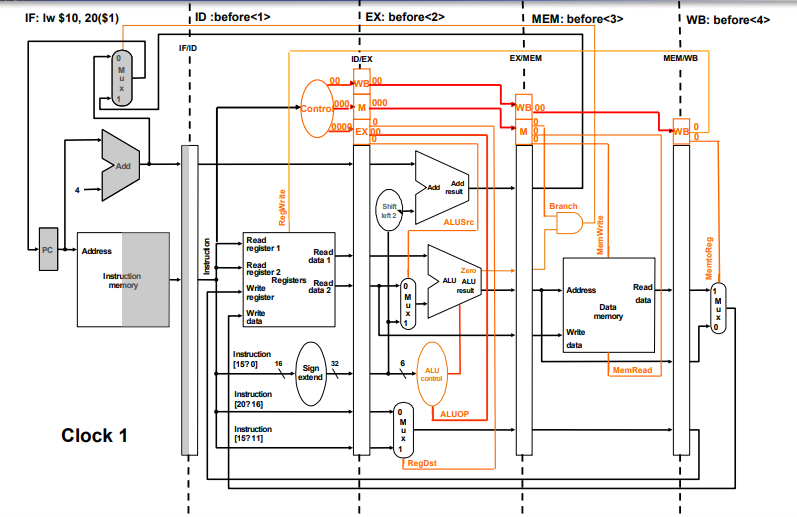

● CLK 1

- 해당 PC값에 해당하는 Inst를 읽고 그걸 ID단에 넘겨주기 위해 Register에 넣는다.

- PC+4

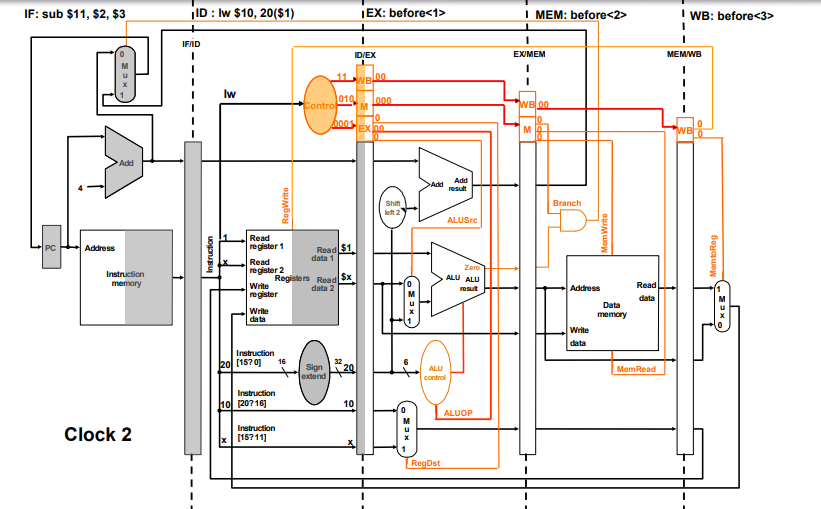

● CLK 2

- ID 단에서 Inst가 LW인 것을 읽고, Control signal을 만들어냈다.

ID 단에서 Register file에서 값을 읽고, sign extend 도 한 값을 EX단으로 넘겨준다.

- IF 단에서 다음 명령어가 읽히고 ID단으로 넘겨줬다.

● CLK 3

- EX 단에서 LW명령어가 진행되기 때문에 Reg 1값과 Sign Extend값을 더하고 있고

그에 맞게 생성된 Control signal 값 덕분에 정상적으로 돌아가는 중이다.

- ID 단에서는 Sub 명령어에 맞는 Control signal 생성 및 sub 명령어를 위한 Reg값 read

- IF 단에서는 그 다음 명령어를 읽고있음.

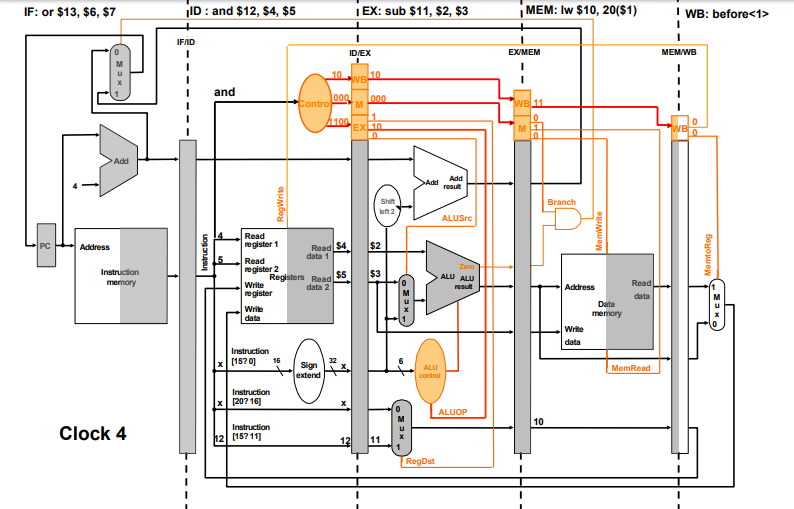

● CLK 4

- MEM 단에서 LW가 Data Mem에 있는 값을 읽음.

- EXE 단에서 Sub가 읽은 값들을 빼는 연산을 하는 중

- ID 단에서 Register에서 연산에 필요한 값들을 읽는 중 + Control signal 생성

- IF 단에서 그 다음 명령어 fetch 중

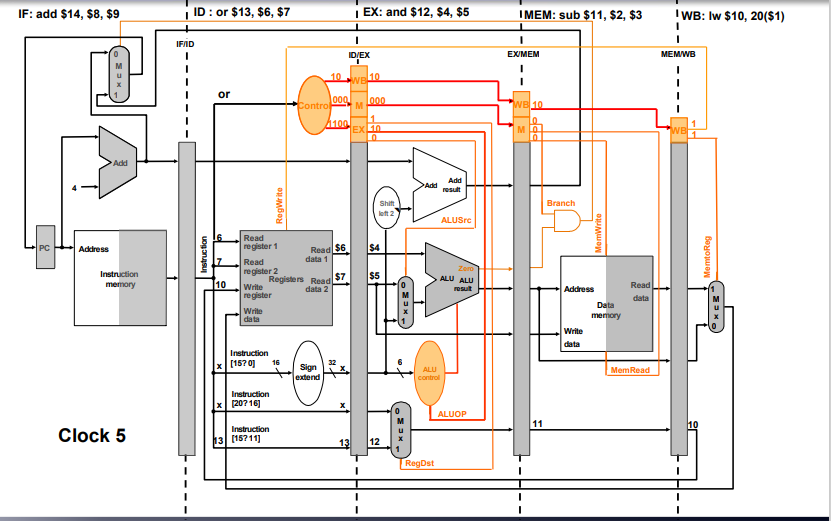

● CLK 5

- WB 단에서 LW가 Data Mem에 있는 값을 Write Register에 적어주기 위해 넘기고 거기에서 씀.

Control signal에 맞춰서 작성.

- Mem 단에서 Sub가 할 건 없음. WB으로 넘겨주기 위해 기다림

...

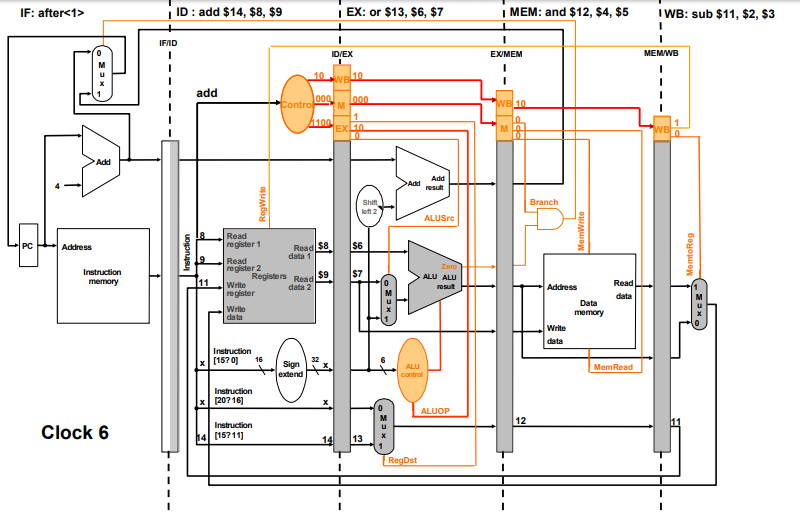

● CLK 6

- EXE에서 연산한 결과를 Write Register로 넘어가서 작성한다.

Summary

[ 성능 비교 ]

Throughput : 시간을 정해놓고 그 안에 명령어를 얼마나 실행하느냐

Latency : 하나의 명령어를 할 때 시간이 얼마나 걸리느냐

Instruction throughput: 그냥 하나의 CLK cycle에 명령어 몇 개가 실행되느냐 생각하면 될 것 같다.

직관적으로 이해하기 쉬우려면 [ 1/CPI ] 로 생각하셈

CLK을 여러 개로 쪼개느냐 크게 한 덩이로 하느냐 또 나눔

1개 명령어 실행하는데 여러 CLK이 필요한지 1개면 되는지로 나누고,

Hardware ( Adder / Mem )을 공유하는지 , 구체적으로 역할에 따른 Hardware를 나누어 놨는지로 또 나눌 수 있다.

(출처)

한동대학교 용환기교수님 - 컴퓨터구조

'2학년 2학기 > 컴퓨터 구조' 카테고리의 다른 글

| [ 컴퓨터 구조 ] 11주차 makeup 문제 (0) | 2023.11.11 |

|---|---|

| [ 컴퓨터 구조 ] 18. Hazard (0) | 2023.11.06 |

| [ 컴퓨터 구조 ] 16. Datapath - Pipeline (1) | 2023.11.02 |

| [ 컴퓨터 구조 ] 15. Datapath - Single/Multi CLK Cycle (강의 multi 2) (1) | 2023.10.29 |

| [ 컴퓨터 구조 ] 14. Datapath - Single Path (0) | 2023.10.24 |