오래 못 할 짓 하지 않기

[ 컴퓨터 구조 ] 23. Virtual memory 본문

Virtual memory

● 가상 메모리 사용 이유

1) 효과적이고 안전하게 Main Mem을 사용, 공유하기 위해

2) 제한된 크기의 Main Mem에서 프로그램이 돌아가는 걸 방지하기 위해서

따라서 Virtual 메모리는 Main mem에 직접 접근하는 방식이 아닌

Virtual mem에 Virtual address로 저장하여, Main mem안에 있는 physical address에 접근한다.

이렇게 주소를 Virtual address를 통해서 접근하는 방법을 Protection 이라고 한다.

Virtual Memory 를 사용하면, 여러 process들이 작동하면서 memory를 공유할 수 있다.

특징

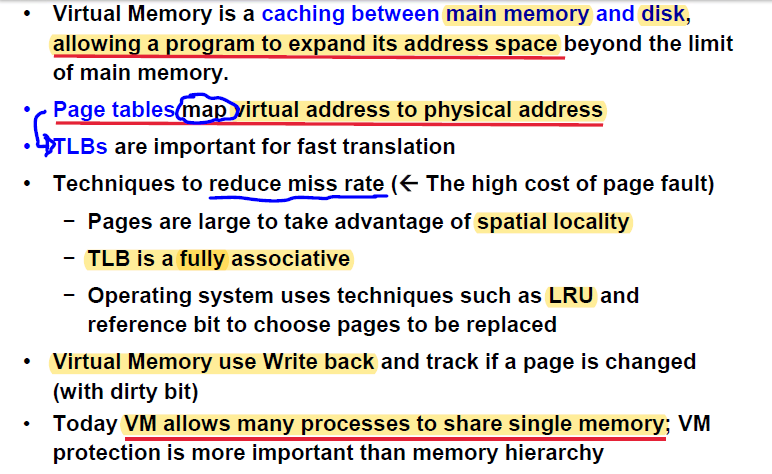

● Virtual Mem은 위 사진에서 Disk와 Mem 사이에서 작동한다.

● 2개의 Level로 작동을 함

1) Primary : DRAM

2) Secondary : Hard Disk

● OS가 메모리를 공유 가능하게 하고, 각각의 process들로부터 program을 보호한다.

● Virtual Mem의 메인 목적은 공유를 위한 Protection이다.

● Virtual Address는 프로그래머에 의해 사용되고, process 내의 메모리 주소를 나타내기 위해 사용된다.

Physical Address는 hardware에 의해 사용되고, 그 주소 자체에 access한다.

● 메모리가 더 있는 것 처럼 사용할 수 있다.

Virtual Mem은 진짜 mem이 아니라, 가상의 개념같은 것이기에 더 많이 접근 가능

virtual = 2^32 개 표현 가능

physical = 그거보단 적음

physical mem보다 모든 작업의 mem도 크고 (먼말이지)

각 작업의 주소를 나타내는 크기도 더 크다.

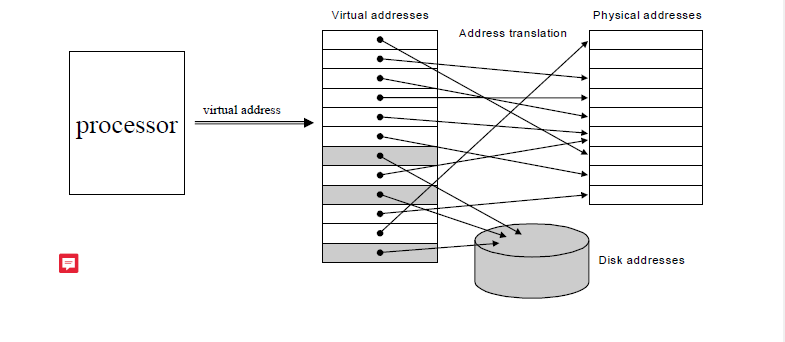

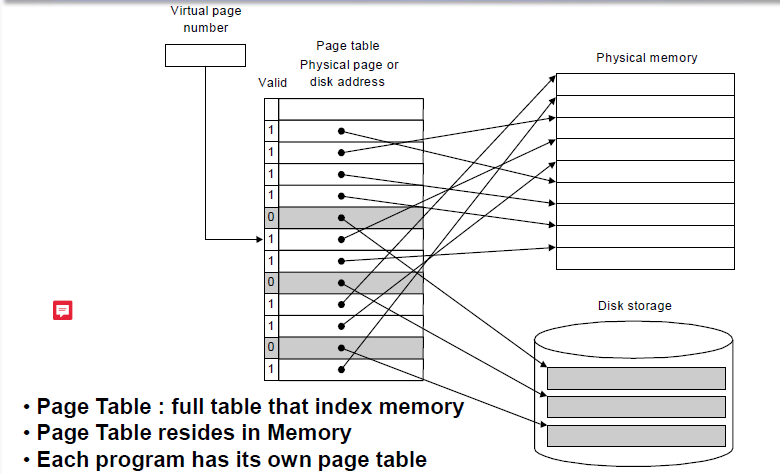

위 사진을 분석해보자

virtual mem의 일부는 [ physical mem의 address ]를 가리키고

그 중 잘 사용하지 않는 일부는 [ hard disk address ]를 가리킨다.

이렇게 하면 processor가 physical mem보다 더 많은 용량을 요구해도,

virtual의 용량만 ㅇㅋ면 데이터를 physical mem과 hard disk에 두고 주고받으면서 작업 가능

그 과정에서 필요한 기술이 Address Translation 이다.

P mem의 주소를 Virtual 이 갖고있다가 쓰일 때 link해주는 것

Processor가 Virtual mem에 address를 주고, 그 주소에 맞는 physical mem 주소가 있으면 그걸 mapping해준다.

이 과정을 address Translation이라고 함.

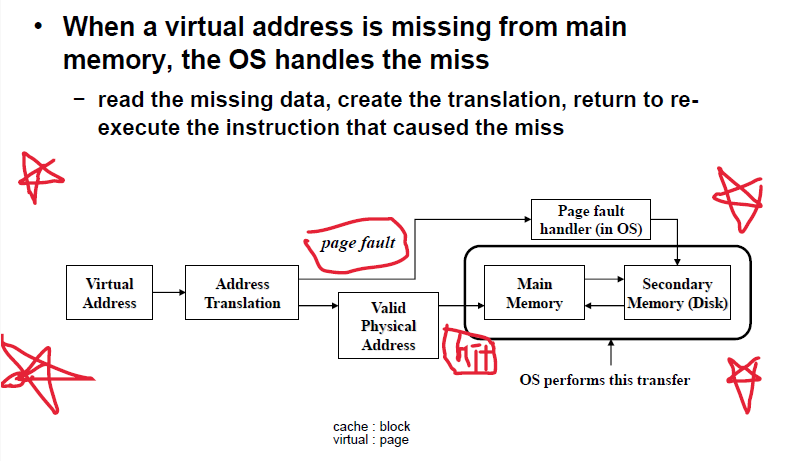

알아둘 것 :

Cache에서 데이터 단위 : Block

Virtual에서 데이터 단위 : Page

Cache에서 데이터가 없으면 : Miss

Virtual 에서 데이터가 없으면 : Fault

작동하는 방식을 그림으로 보면 위와 같다.

Virtual mem에 virtual address를 주고, 그 값이 유효하다면 physical address로 가는 주소를 준다.

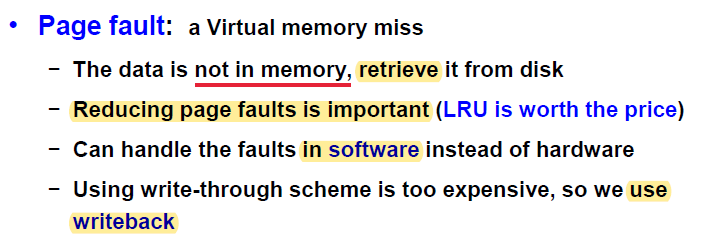

Virtual mem에 데이터가 없으면.. = Page fault

● 데이터가 메모리에 없다면, Disk에서 가져온다.

● Page fault를 줄이는 것이 Performance 측면에서 중요하며

이를 위해서 LRU가 가장 가성비 있었다.

● fault 는 software에서 처리한다.

● Writeback을 사용한다. (write-trough는 너무 비쌈)

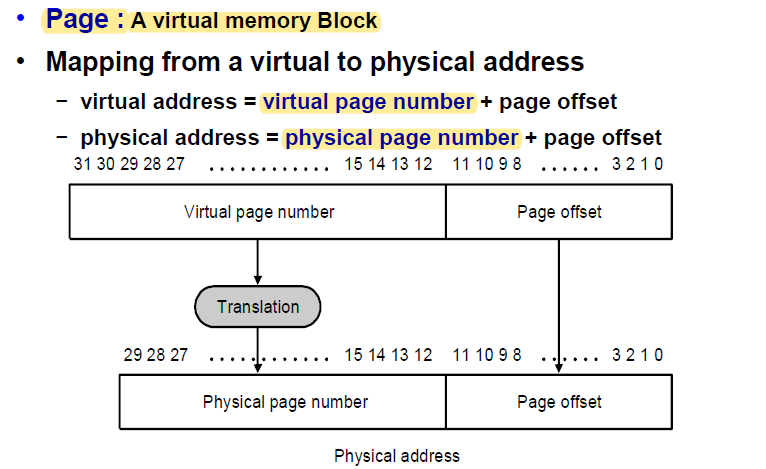

Page table

cache 형태랑 비슷하다.

● valid bit = 1 > 찾는 page가 physical mem 에 있다.

● valid bit = 0 > 찾는 page가 hard disk에 있다.

.

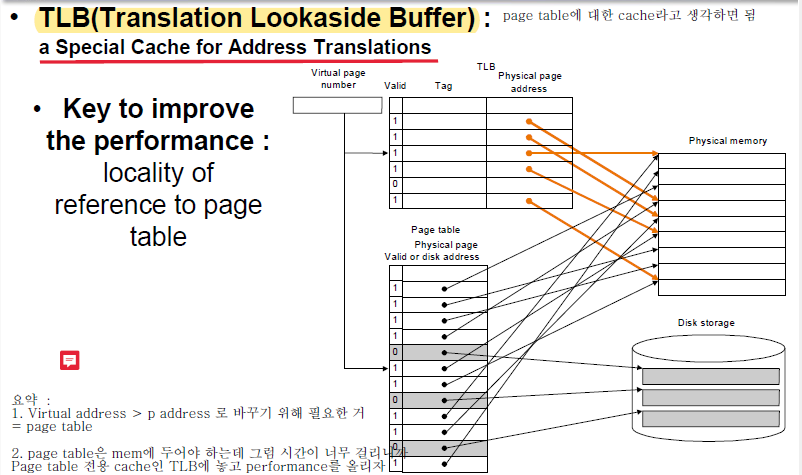

TLB

TLB는 Virtual mem의 Page table전용 Cache라고 생각하면 편하다.

● 생긴 배경

: page table을 계속 reference하려면 시간이 너무 많이 든다.

> 일부를 cache에 넣어둔다. = 이 cache = TLB

(이거 전용 cache임)

cache도 inst용, data용, page table용이 있다.

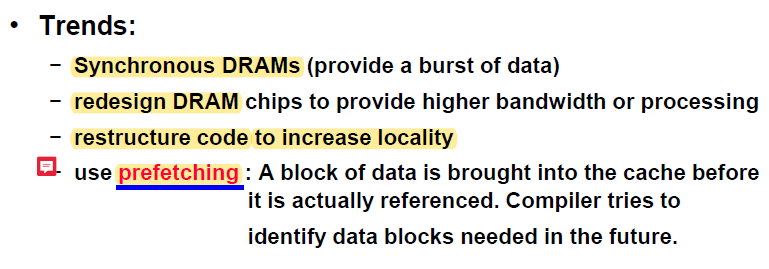

Processor의 속도는 매우 빨라지는데, 그에 비해 DRAM과 Disk의 속도는 아직 발전이 더딤

: 그 차이를 줄이는 것이 Design의 목표

요즘 추세

prefetching : 데이터가 없는지 보고 가는 게 아니라,

미리 명령어들을 분석하고 필요할 거 같은 걸 가져와두는 것

천천히 읽어보고 이해 안 되는 거 있나 보기

(참고)

https://ttl-blog.tistory.com/1097

(출처)

한동대학교 용환기교수님 - 컴퓨터구조

'2학년 2학기 > 컴퓨터 구조' 카테고리의 다른 글

| 컴구 기말 (0) | 2023.12.07 |

|---|---|

| [ 컴퓨터 구조 ] 24. File I/O (0) | 2023.12.02 |

| [ 컴퓨터 구조 ] 22. Cache performance (0) | 2023.11.26 |

| [ 컴퓨터 구조 ] 21. Direct ( cache ) (0) | 2023.11.20 |

| [ 컴퓨터 구조 ] 12주차 makeup 문제 (0) | 2023.11.16 |