오래 못 할 짓 하지 않기

논리 설계 19 본문

x F/F (+@)를 가지고 y F/F 만들기

순서 :

1. Truth table을 만든다

--> Q에서 Q* 상태로 만들기 위해서 그 안에 있는 F/F의 behavior를 고려 해서 안에 들어있는 F/F의 input을 만들어준다.

2. *Q 다음에 있는 것들에 대한 카르노맵을 만들어준다.

입력은 y F/F + Q

3. 안에 게이트는 그대로 냅두고 y F/F로 가는 logic gate들을 만든다.

ex 1 )

풀이

1) truth table을 먼저 만든다

우선 JK = 0 0 이면 No change이기 때문에 최종 출력은 Q인 상태로 되어야한다.

Q가 0이면 *Q = 0

Q가 1이면 *Q = 1

이런 경우에 D F/F의 특성을 생각해보자. 들어온 대로 내보내기 때문에

D F/F의 Input은 *Q의 값을 그대로 해주면 된다.

2) 카르노 맵

이렇게 진리표를 만들었으면 그걸로 카르노 맵을 만든다.

출력 = D = JQ' + K'Q 라는 식이 나온다.

3) 그거에 맞게 회로를 그린다. ( 안에 들어간 F/F는 냅둔다 )

ex 2 )

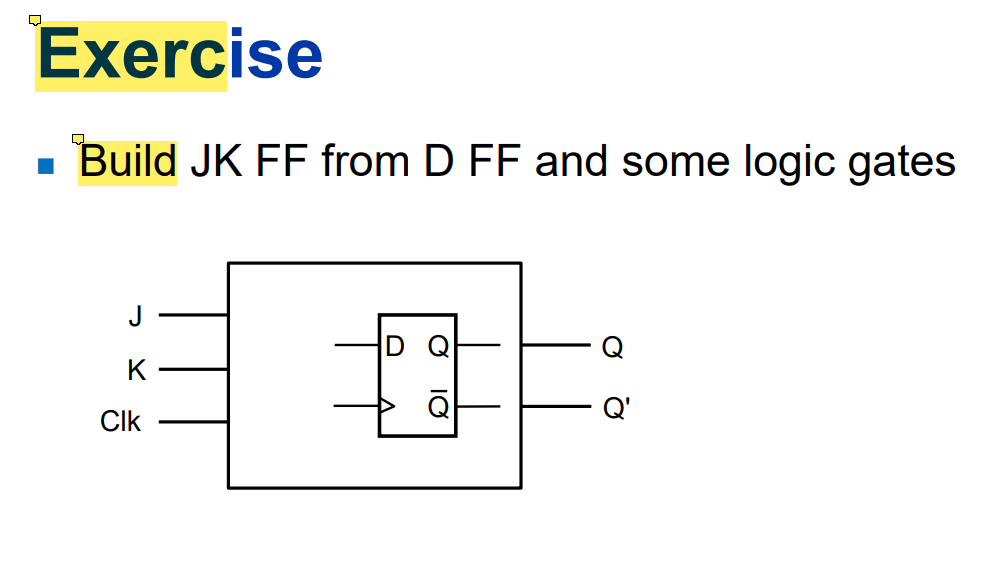

D F/F --> JK F/F + 게이트 몇 개 가지고 만들기

사실 진리표만 만들 줄 알면 끝남

ex 3)

T = KQ + JQ'

순차 회로 분석

1) D F/F

이렇게 해서 나온 식들로

Moore model로 분석한다

Moore model 특 : 현재 상태만 보고 출력을 결정함.( Input은 다음 상태와 출력에 영향을 끼침)

표 보는 법 설명

- 왼쪽 부분

위에 q1*라고 적혀있으니 그거에 관련된 F/F만 본다는 의미이다.

( 이 사진 말고 그 위에 사진으로 봤을 때 오른쪽 말고 중간에 있는 게이트 보는 거임 )

즉, 고려해야할 식이 q1* = D1 = q1 q'2 + x q'1

이고 옆에 q1q2를 거기에 대입하면 된다~!

- 오른쪽 부분

게이트 전체를 고려함.

D1 = q1 q'2 + x q'1

D2 = x q1

이거 두 개를 생각하고, 표에도 그려놓았듯 숫자 두 개는 D1 D2 로 나타내는 거다.

- 아래 부분

현재 상태에 따라 출력이 결정되는 것이다.

00일 땐 1을 출력하고, 입력에 의해 다음은 어느 상태로 갈지 정한다.

2) JK F/F

𝐽𝐴 = 𝑥

𝐾𝐴 = 𝑥𝐵′

𝐽𝐵 = 𝐾𝐵 = 𝑥 + 𝐴′

위의 식에 대입을 하면서 풀어보자.

AB = 0 0 , x=0 --> JA = 0 , KA = 0 and JB = 0+1 , KB = 0+1

- A에 관해서는 J K = 00 --> No change --> 0이 들어오고 No change = 0

- B에 관해서는 J K = 11 --> Toggle --> 0이 들어오고 Toggle = 1

이런 식으로 풀면 됨

이건 살짝 복잡할 수도 있음

우선 왼쪽 표랑 오른쪽 표를 같이 봐야하는데

왼쪽 표를 보자. A B가 00 이고 x가 0이다. 여기까진 오른쪽 표가 필요없음

오른쪽 표는 [ 출력 ] 과 [ 다음 상태 ]를 보기 위해 봐야한다.

A B 00이고 x가 0일 때 --> 출력 : 0 / 다음 상태 : 01

이렇게 풀면 된다 이말

그리고 마지막 부분이 아니라 10과 11부분에서는 x의 값에 상관없이 출력이 1이 되기 때문에

다음 상태에 따라 어떻게 될지 모르긴 하지만, 당장의 출력은 x값 상관없이 뭐가 나오는지 알 수 있는 경우도 있다.

Mealy Model

출처 : 한동대학교 고윤민 교수님 - 논리설계 PPT

'2학년 1학기 > 논리 설계 ( Logic design )' 카테고리의 다른 글

| 논리 설계 21 (0) | 2023.05.21 |

|---|---|

| 논리 설계 20 (The Design of Sequential Systems) (0) | 2023.05.14 |

| 논리 설계 18(Flip-Flop) (0) | 2023.05.02 |

| 논리 설계 17 (Flip-Flop) (0) | 2023.04.30 |

| 논리 설계 16 (순차 논리 회로 , SR latch, D latch) (0) | 2023.04.25 |