오래 못 할 짓 하지 않기

논리 설계 16 (순차 논리 회로 , SR latch, D latch) 본문

순차 논리 회로

현재 입력 과 + 그 때의 상태 에 따라 출력이 나오는 회로

(비교)

조합 논리 회로 VS 순차 논리 회로

메모리가 없다 || 메모리가 필요함

Output : 현재 Input에 달렸음 || 현재 Input + 이전 Condition

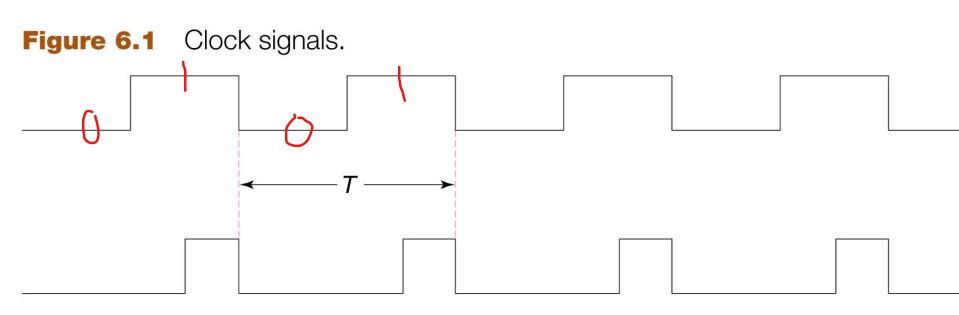

- Clock (CLK)

: 0과 1을 왔다갔다 하는 신호

- 주기(T) : 한 번 내려갔다가 다시 올라오는데 걸리는 시간or길이

- 진동수 : 1/T

메모리가 어떻게 돌아가는지 느낌만 보자

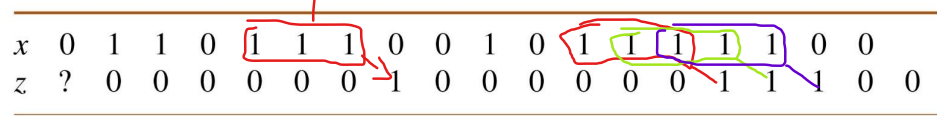

예) 입력에 1이 연속으로 '최소 3개'가 있어야 1이 출력됨.

이 때 앞에 1이 연속으로 몇 개 들어왔는지 어떻게 알 수 있나?

State(상태)가 메모리에 저장된다. 들어온 정보들을 메모리에 저장하여 State로 남아있음.

Moore system : Output이 state의 영향을 받음

다음과 같은 표를 보면 이해하기 쉽다.

출력은 현재 상태 = D일 때 1이 출력되는 회로임.

현재 상태가 무엇인지에 따라 출력이 1인지 결정되지, 현재 상태 외에 x가 뭐가 들어오는지에는 크게 영향이 없다.

그림을 보면 출력이 알파벳과 같은 위치에 있음

Mealy system : Output이 state와 + input의 영향을 받음

그림을 보면 A나 B에 출력이 있는 게 아니라 나가면서 출력이 나옴.

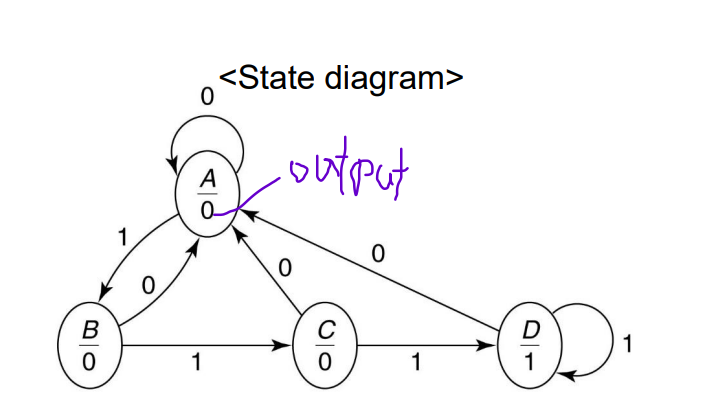

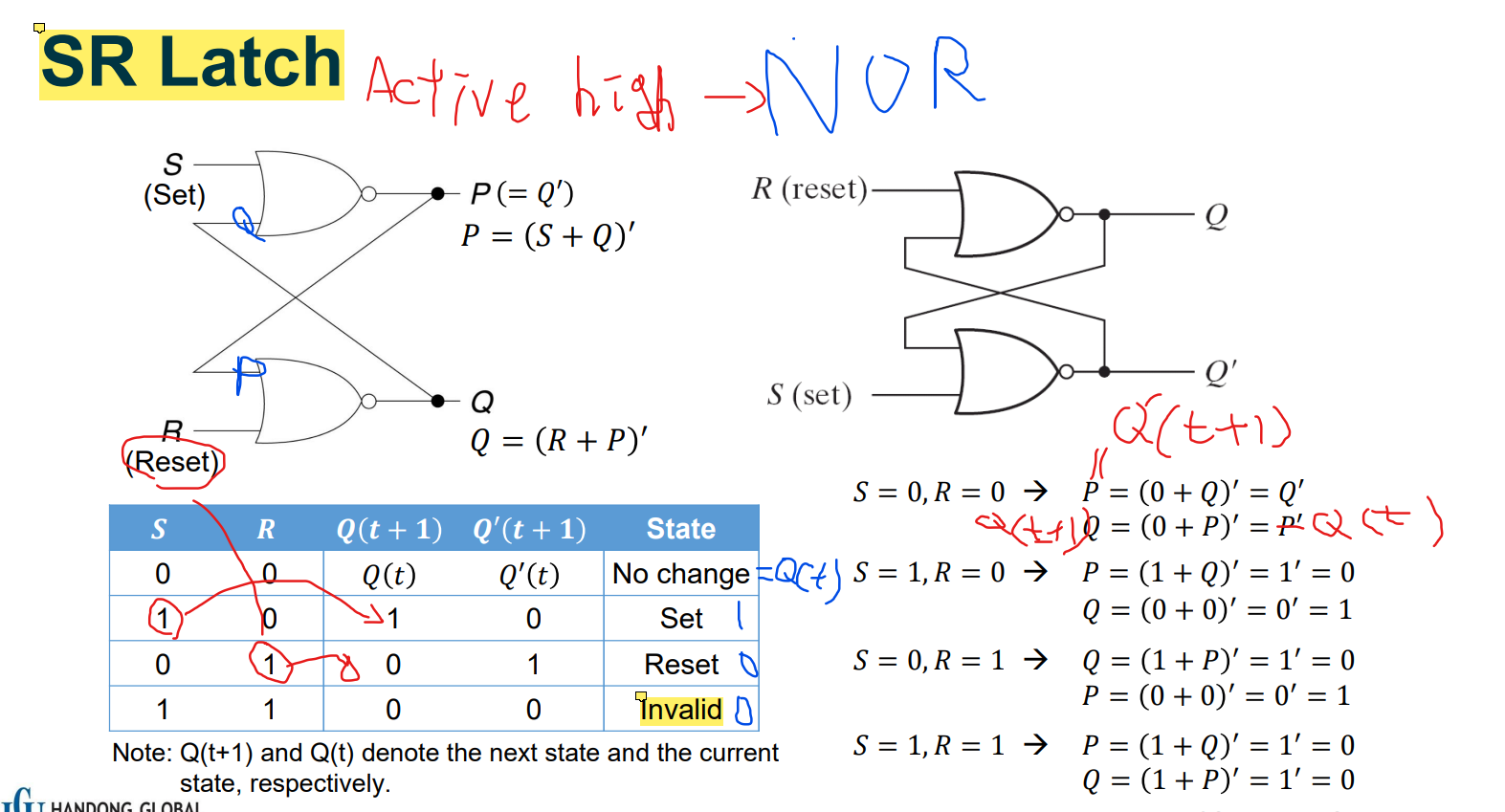

Latch

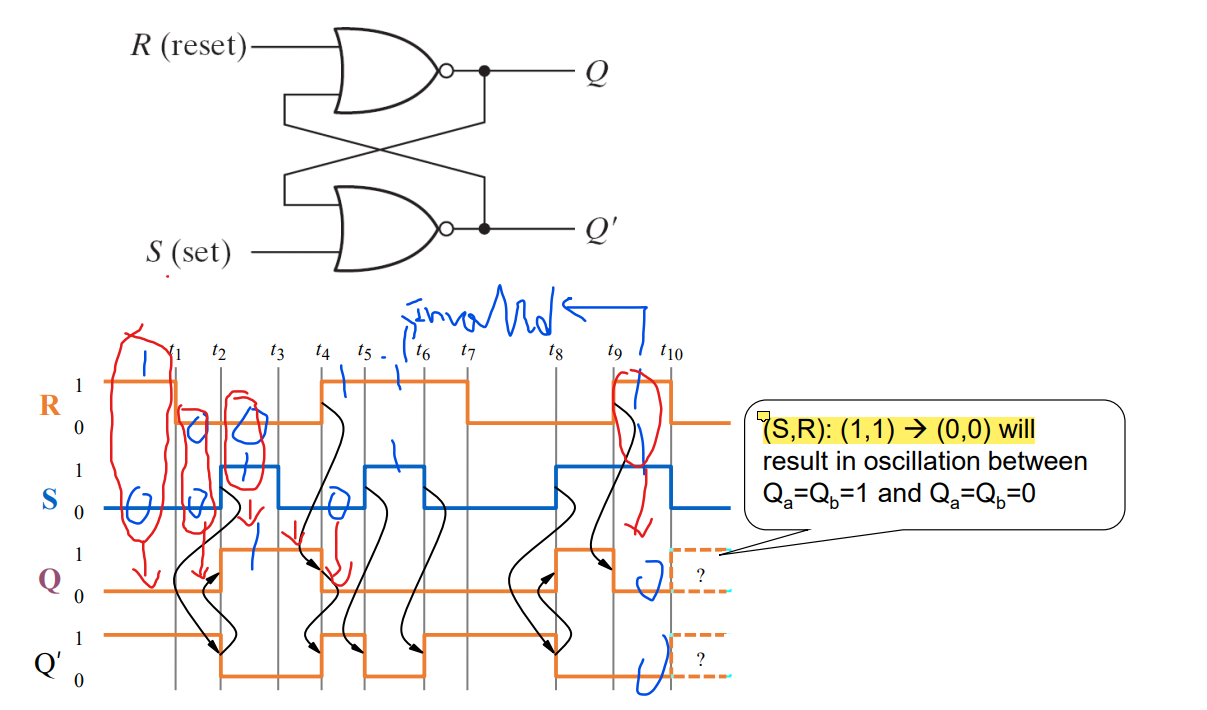

Input: Set / Reset (set = 1로 만드는 input / Reset =0으로 만드는 input)

P = Q'(t+1) / Q = Q(t+1)

우선 회로부터 설명하자면 위에 NOR 게이트에는 S와 (R'+P)' 가 들어간다.

P = (S+Q)'

밑에 게이트로는 R이 들어오고 P가 나가나가 왔으니 그대로 P가 들어왔으므로

(R+P)' 인데 P=Q'이므로 Q = (R+P)'

| S | R | Q(t+1) | Q(t+1)' | state |

| 0 | 0 | Q(t) | Q(t)' | No change = Q(t) |

| 1 | 0 | 1 | 0 | 1 = set |

| 0 | 1 | 0 | 1 | 0 = reset |

| 1 | 1 | 0 | 0 | Invalid = 0 |

S와 R의 값에 따라, 전 상태 그대로 유지/ 1 / 0 / Invalid (=0) 이 정해진다.

NAND로 만들면 Active low 도 가능하다.

이 경우에 진리표를 보면 No change 와 Invalid 가 나오는 입력이 바뀌고

Set과 Reset으로 되는 입력도 바뀐다.

Latch에 관해서 그래프 그리기 시험에 나올 듯

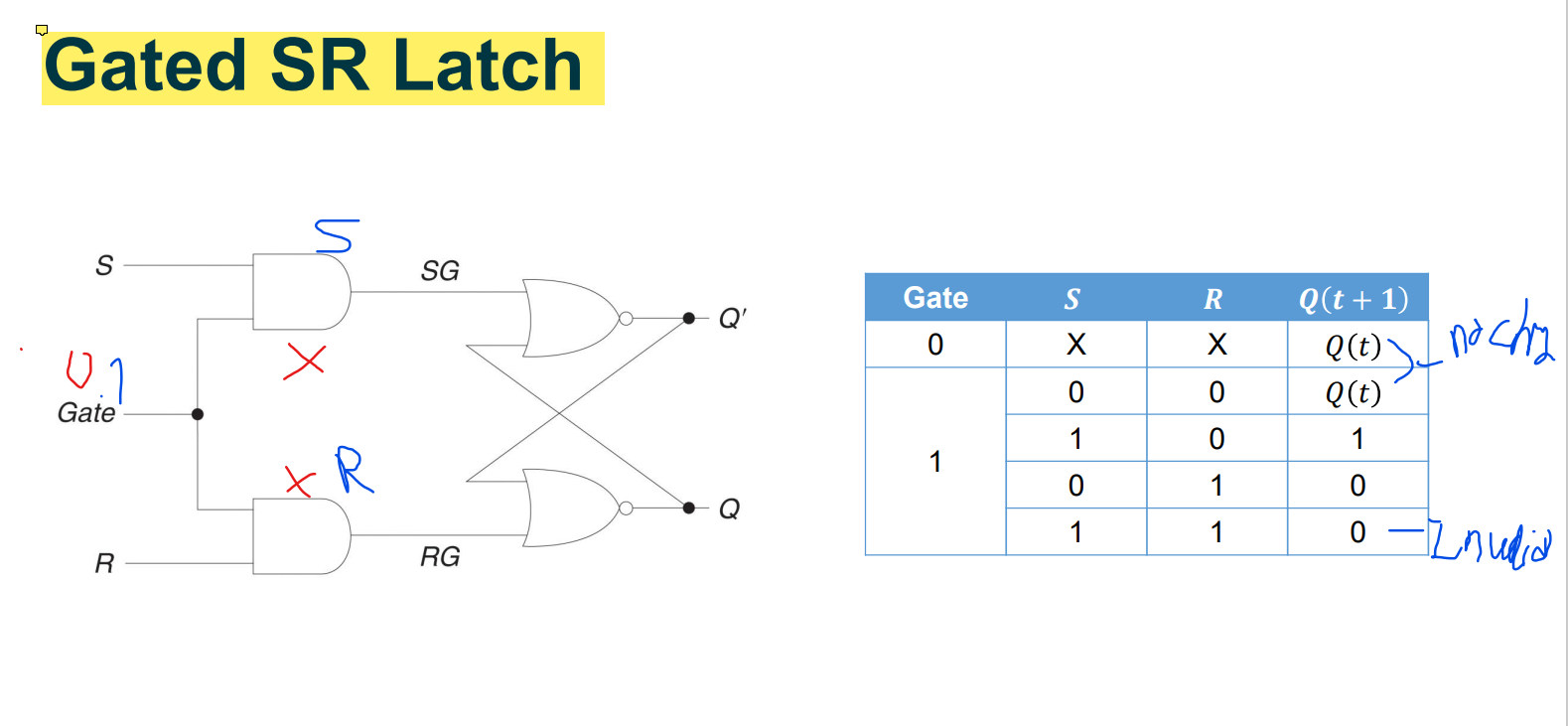

SR Latch에 And Gate를 달아서 Input을 못 받게(= No change) 할 수 있음.

분석해보면 Gate가 0이면 새로운 Input이 없기 때문에 Q(t+1) = Q(t) (No change)

- Gate 1일 떈 일반 Latch랑 같다.

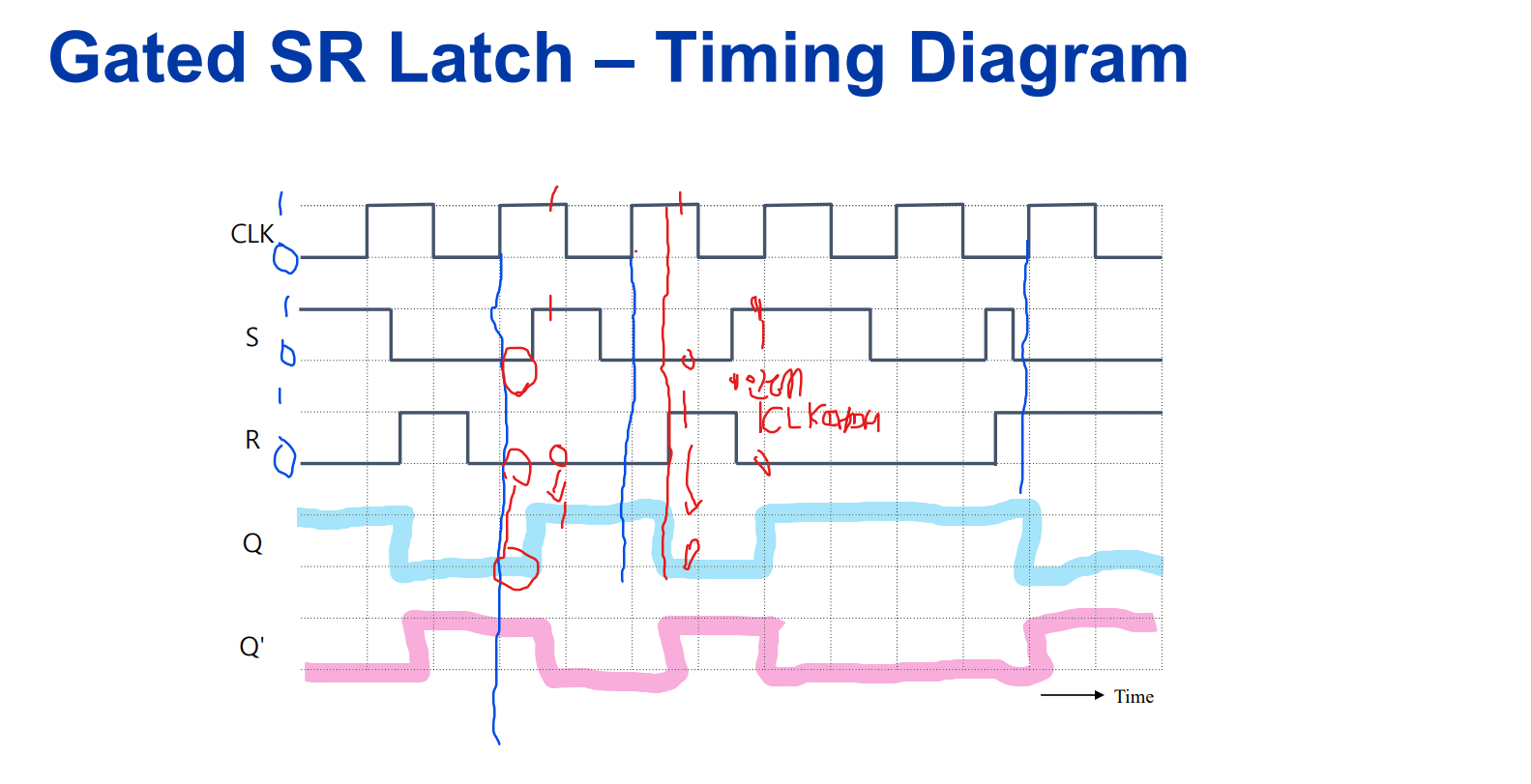

SR Latch 타이밍 그램을 보면 위와 같다.

가장 중점으로 봐야하는 건 CLK의 상태이다.

CLK = 0일 땐, 0이 될 때의 상태(Q(t))로 Q(t+1)가 유지되고,

CLK = 1일 땐, S 와 R의 조합에 따라 변한다고 보면 된다.

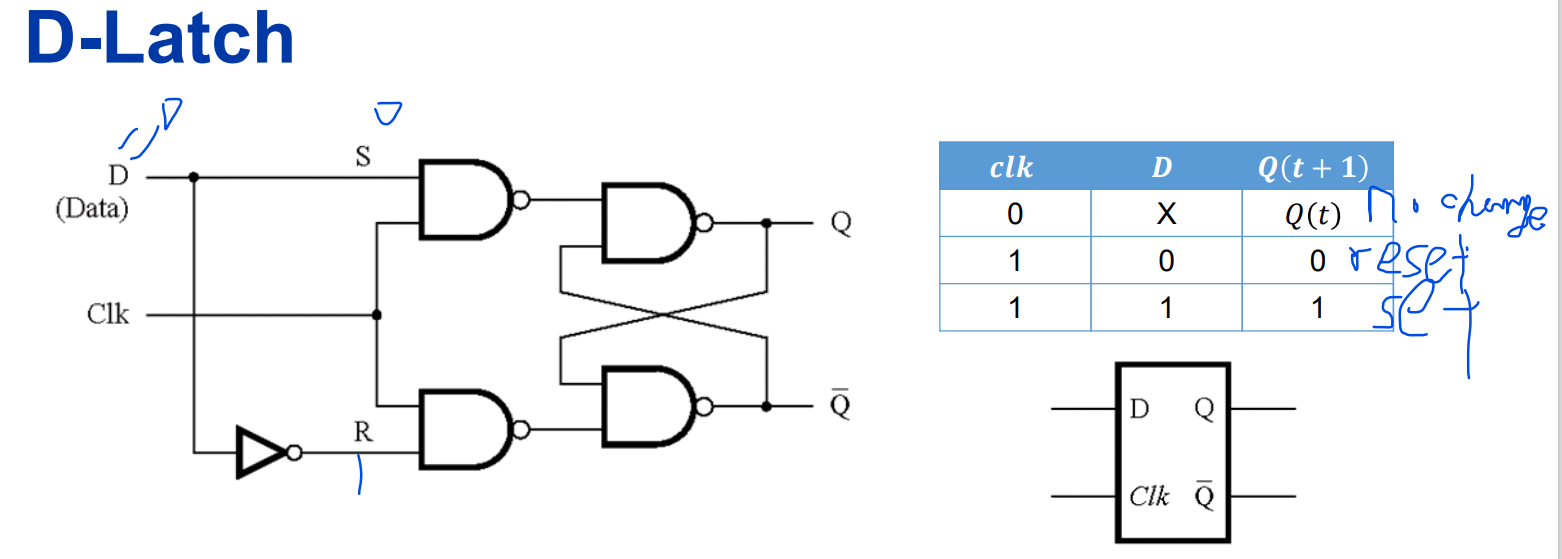

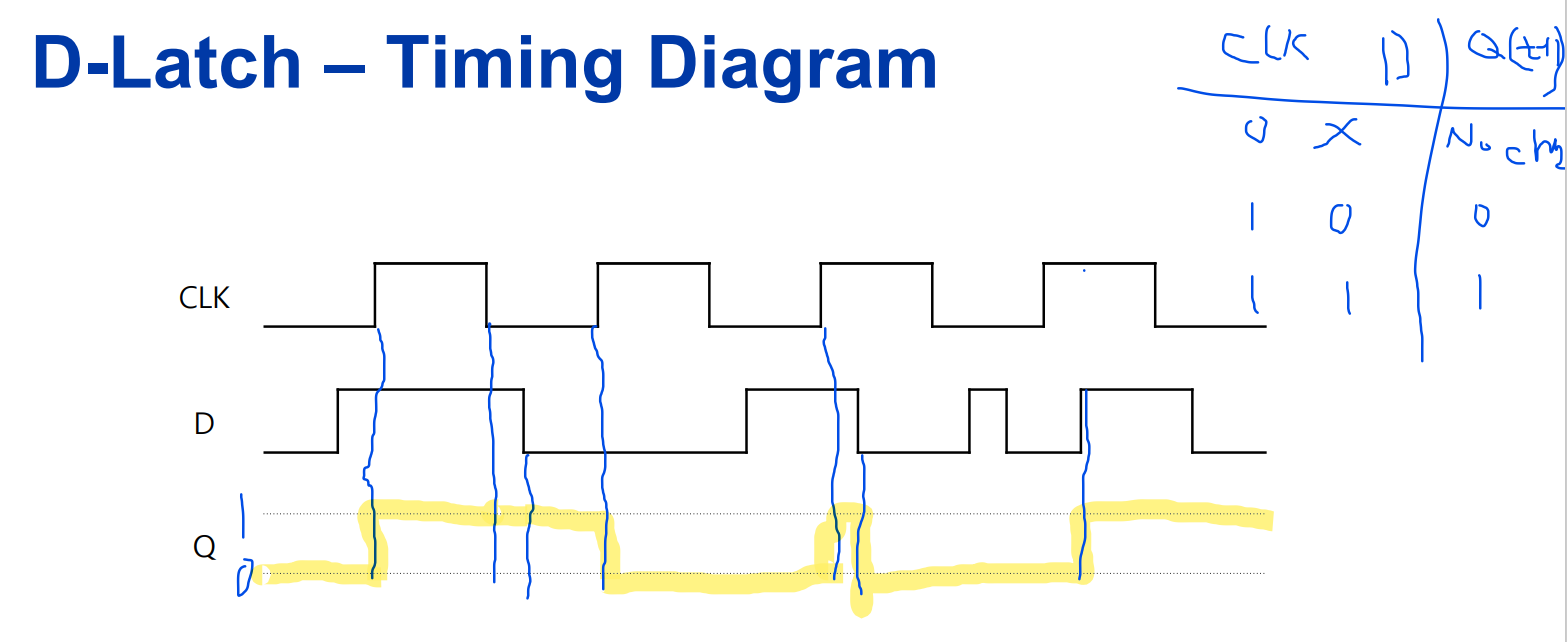

D Latch

SR Latch + Sigle Data input

D에 상태에 따라 S를 취할지 R을 취할지가 정해짐

마찬가지로

CLK이 0일 땐 , Q(t) << CLK이 0이 될 때의 상태 == Q(t+1)

CLK이 0일 땐 , D의 값에 따라 상태가 따라감.

Latch timing problem

-> CLK이 1이면, 그 동안 출력이 010101010101계속 바뀌어서 그거 해결하려고 이거 한다는데 영상보고 이해하기

https://ttl-blog.tistory.com/623

Register = 상태 저장공간

해결하려면 clk에 En달고

register를 한 칸씩 뒤로 밀

출처: 한동대학교 고윤민 교수님 - 논리설계 PPT

'2학년 1학기 > 논리 설계 ( Logic design )' 카테고리의 다른 글

| 논리 설계 18(Flip-Flop) (0) | 2023.05.02 |

|---|---|

| 논리 설계 17 (Flip-Flop) (0) | 2023.04.30 |

| 논리 설계 15 (PROM PAL PLA) (1) | 2023.04.18 |

| 논리 설계 14 (0) | 2023.04.14 |

| 논리 설계 13 (Comparators , Encoder / Decoder ) (0) | 2023.04.11 |