오래 못 할 짓 하지 않기

[ 컴퓨터 구조 ] 8. (Multiple Cycle) Multiple Cycle 제어부 (Control Unit) 본문

2학년 2학기/컴퓨터 구조

[ 컴퓨터 구조 ] 8. (Multiple Cycle) Multiple Cycle 제어부 (Control Unit)

쫑알bot 2023. 7. 5. 15:52728x90

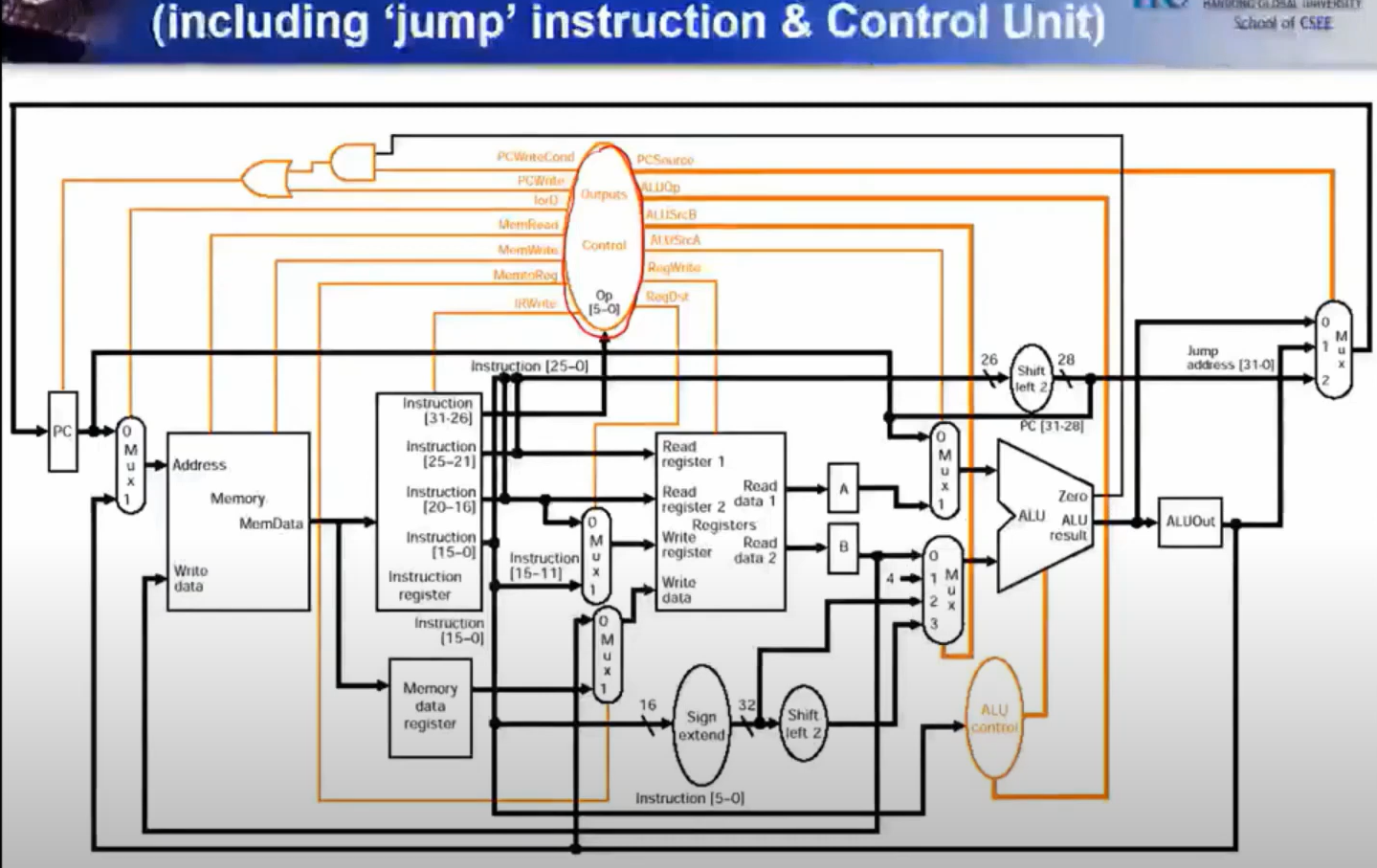

Multiple Cycle Control Unit

사진에 보이는 주황색 원이 Control Unit이다.

Single Cycle 에서 다루었듯이 이건 Finite state machine이다. (상태로 제어함)

이걸 보고 R타입일 땐 어떤 게 0,1 (Or 2,3까지) 켜지는지 할 줄 알아야 한다.

이전 시간에 배웠던 걸 가져와서 Finite state 로 표현해 보자

초기 상태 = S0 (fetch 할 예정)

S1 에서 R타입이다 = 가장 위

S1 에서 I타입이다 = 가운데

S1 에서 Branch타입이다 =가장 아래

이런 식으로 표현 가능하다.

예제 풀어보기 (9:41)

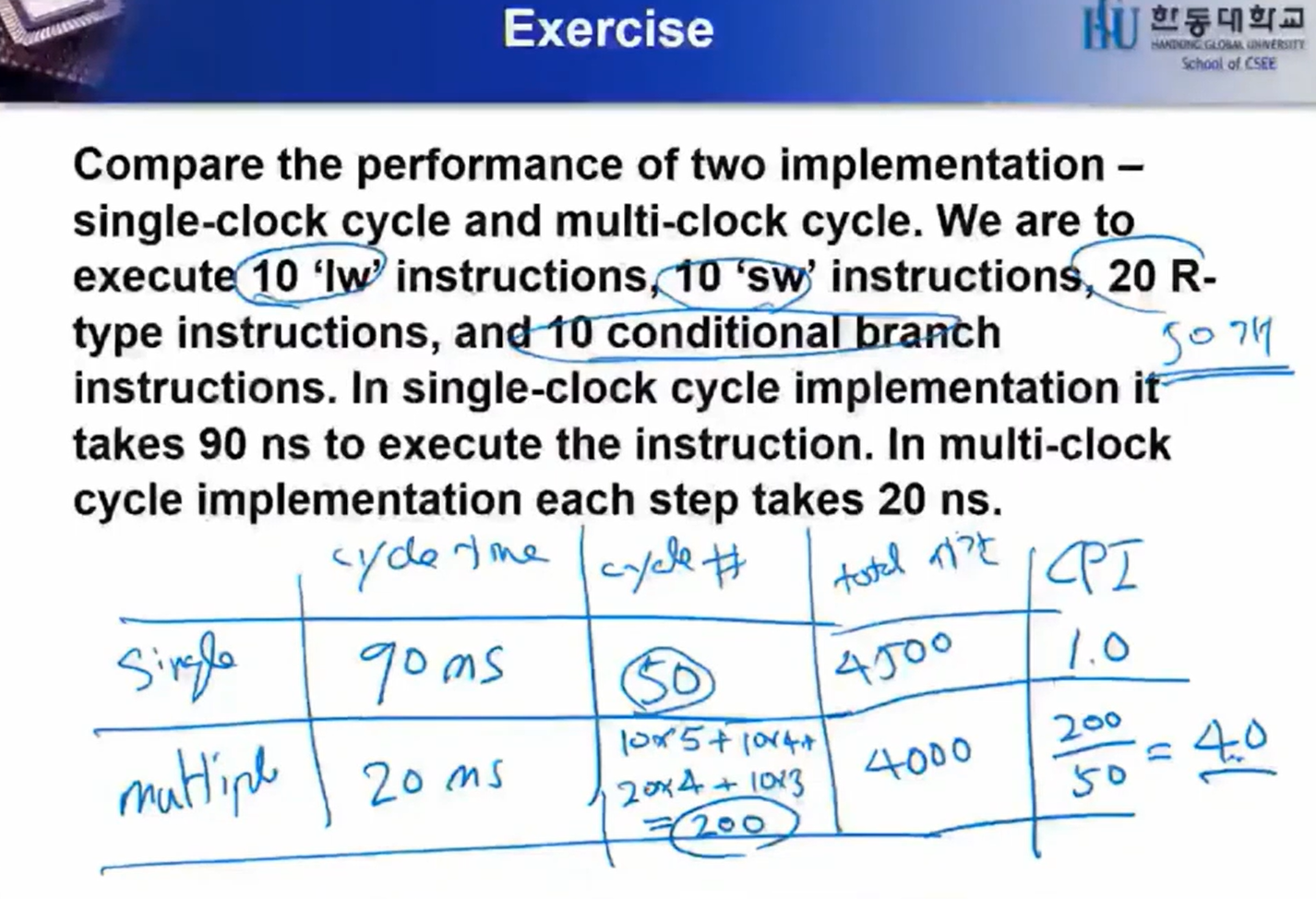

Single clock cycle ↔ Multi clock cycle 비교

조건 1. LW inst 10번 실행 + SW inst 10번 실행 + R type inst 20번 실행 + Branch inst 10번 실행

조건 2. 실행하는데 Single clock cycle은 90ns 가 걸렸고, Multi clock cycle는 각 과정당 20ns가 걸렸다.

- Cycle Time

Single : 90 ns

Multi : 20 ns - Cycle 개수

Single : 50 ns ( Instruction 의 개수들을 합하면 된다 )

Multi : 200 ns ( LS (= 10 * 5 ) + SW (= 10*4) + R (=20*4) + Branch (=10*3) )

LS = 5 steps / SW, R = 4 steps / Branch = 3 steps - Total 시간

Single : 90ns * 50 = 4500ns

Multi : 20ns * 200 = 4000ns - CPI

Single : 1.0

Multi : Cycle 갯수 / 명령어 개수 = 200/50 = 4

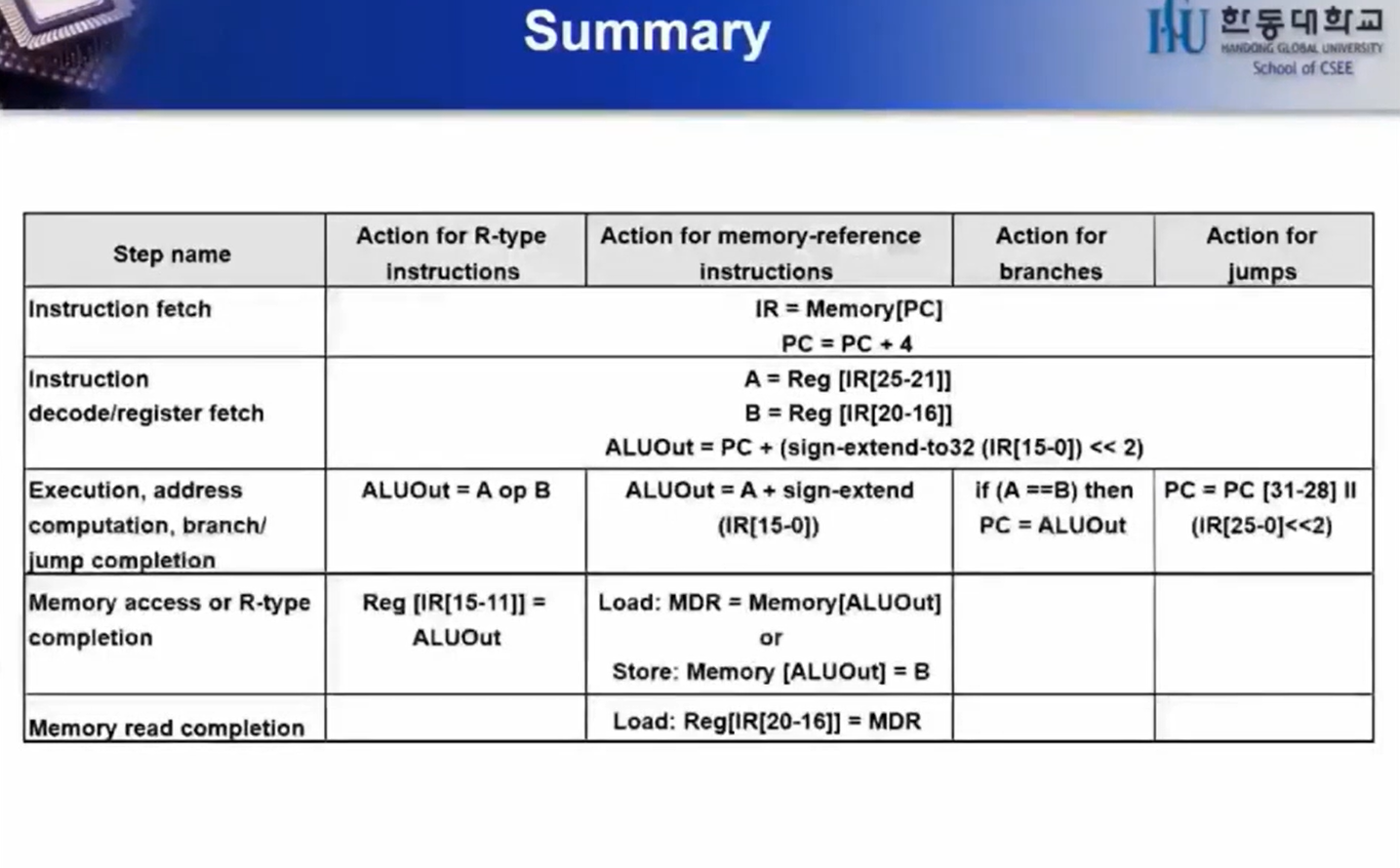

Summary

출처 : 한동대 SW 중심대학

'2학년 2학기 > 컴퓨터 구조' 카테고리의 다른 글

| [ 컴퓨터 구조 ] 10. Pipeline 적용 (0) | 2023.07.06 |

|---|---|

| [ 컴퓨터 구조 ] 9. Pipeline (0) | 2023.07.05 |

| [ 컴퓨터 구조 ] 7. (Multiple Cycle) 명령어별 Multiple Cycle 실행 (0) | 2023.07.05 |

| [ 컴퓨터 구조 ] 6. (Multiple Cycle) Multiple Clock Cycle (0) | 2023.07.04 |

| [ 컴퓨터 구조 ] 5. Single Cycle 제어부 (0) | 2023.07.04 |