오래 못 할 짓 하지 않기

[ 컴퓨터 구조 ] 7. (Multiple Cycle) 명령어별 Multiple Cycle 실행 본문

Five Execution Steps

- Instuction Fetch // (1~2) 는 무슨 일을 하는지 읽는 단계 , 명령어가 어떤 거냐에 관계없이 공통으로 동작함.

이걸 할 때, [ PC , Memory , Instuction Memory ] 가 일함

ALU는 놀고있음 → 미리 PC+4 작업 시킴 - Instruction Decode and Register Fetch

또 놀고있을 거 대비해서 PC+(imm16) 해놓음 , 혹시 Instuction 이 Branch 일 수도 있으니까. 그거면 바로 branch하게

Target address 미리 계산 - Execution, Memory Address Computation or Branch Completion // (3~5)는 1,2에서 읽은 거 실행하는 단계

- Memory Access or R-Type instuction completion

- Write-Back step

명령어에 따라 몇 번째 step까지 하는지 다름.

ex) ADD

1,2 에서 더하기를 한다는 것과 무엇과 무엇을 더하는지 알 수 있다.

3에서 더하기를 하고 4에서 레지스터에 적은 뒤에 끝낸다.

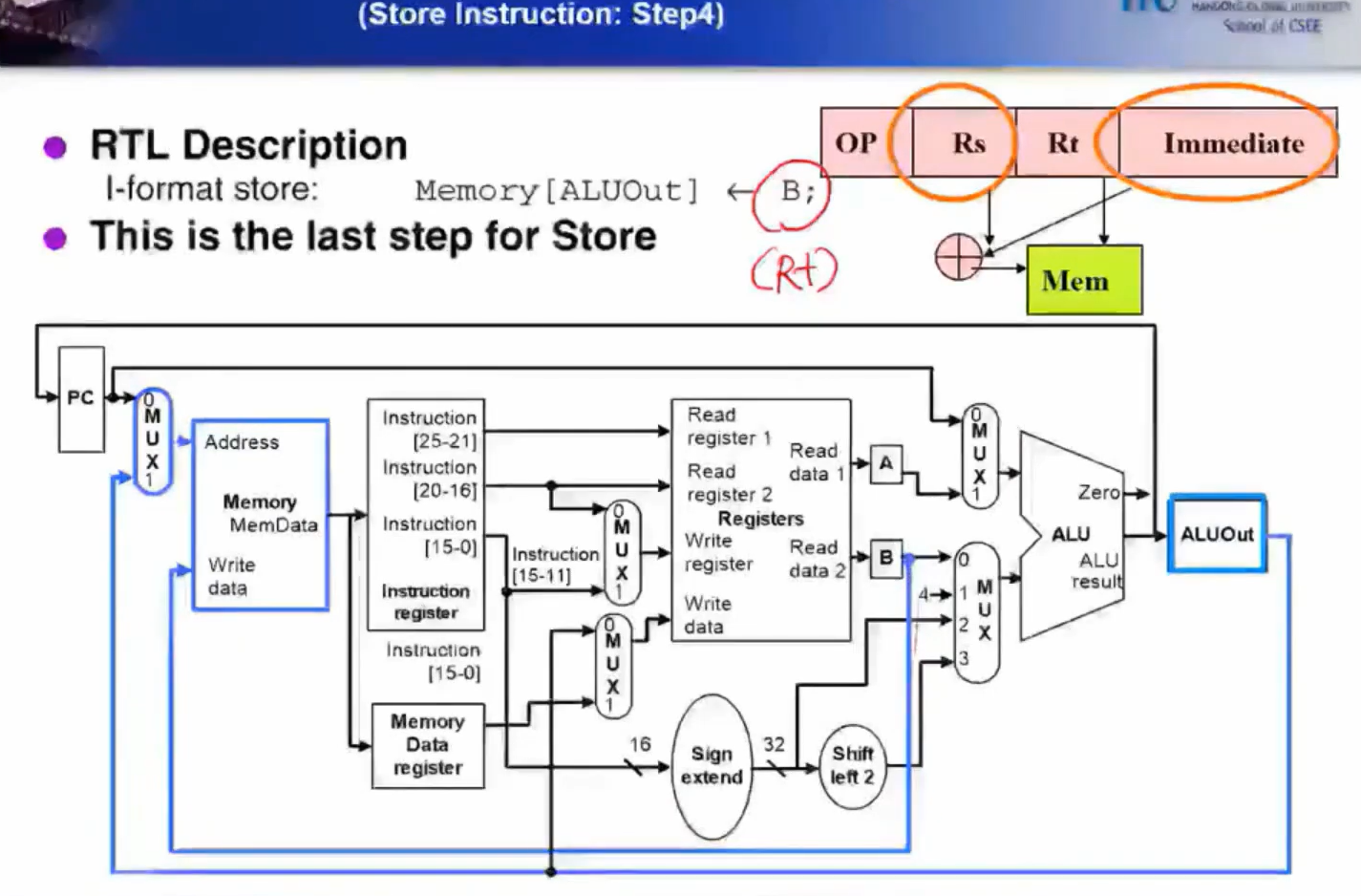

ex) SW

1,2 에서 SW를 한다는 것과 무엇을 Store하는지 알 수 있음.

3에서 Memory 주소를 구하고, 4에서 메모리에 접근하여 write를 하고 끝낸다.

Rs 표현법 : A , Reg [ IR [ 25 -21 ] ]

Rt 표현법 : B, Reg [ IR [ 20 - 16 ] ]

요약하자면

R type

1 CLK : PC값으로 Instruction 을 읽고, PC값 4증가

2 CLK : A register B regisetr에 Rs, Rt 값 담기 , Branch 일수도 있으니 미리 주소 계산해 두기

3 CLK : A와 B를 가지고 ALU에서 Instruction 에 맞게 계산하기

4 CLK : ALUOut에서 나온 값을 Register File에 Write

I type

1 CLK (공통): PC값으로 Instruction 을 읽고, PC값 4증가

2 CLK (공통) : A register B regisetr에 Rs, Rt 값 담기 , Branch 일수도 있으니 미리 주소 계산해 두기

3 CLK : [ 주소 계산 ] A + sign-extend (IR [15-0]); = rs + imm16

4 CLK : (SW일 때) Memory [ ALUOut ] = B; / (LW일 때) MDR = Memory[ ALUOut ] ;

5 CLK : (LW일 때) Reg[ IR [20 - 16] ] = MDR

Branch

1 CLK (공통): PC값으로 Instruction 을 읽고, PC값 4증가

2 CLK (공통) : A register B regisetr에 Rs, Rt 값 담기 , Branch 일수도 있으니 미리 주소 계산해 두기

3 CLK : Branch여부를 판단하여 branch

PC = (A==B) ? ALUOut : PC+4; ( PC값은 , A와 B가 같으면 ALUOut으로 하고, 아니면 PC+4)

각 단계별로 하는 일을 자세히 알아보자

- Instuction Fetch (3:43)

▣ IR = Memory [PC]; 메모리의 PC번째 데이터를 읽고, Instruction register에 저장해라

▣ PC = PC+4; 다음 PC명령어를 가리켜라. - Instruction Decode and Register Fetch (4:44)

▣ A = Reg [ IR [25-21] ]; A, B register에 필요한 값을 미리 받아놓는다.

▣ B = Reg [ IR [20-16] ];

▣ ALUOut = PC + ( sign-extend ( IR [ 15-0] ) << 2 ) ;

↑ Branch 명령어가 들어왔을 수도 있으므로 Branch Target adress미리 계산

+ Decode 명령이 없는 이유 : Decode는 Datapath가 아니라 Control 쪽에서 하기 때문.

3. Execution, Memory Address Computation or Branch Completion // (3~5)는 1,2에서 읽은 거 실행하는 단계

[ Instruction Dependent ] Inst가 뭐냐에 따라 명령어가 달라진다.

1) Memory referenct 일 때 (lw , sw)

▣ A + sign-extend ( IR [ 15-0] ) ; // rs + (imm16) 임

2) R-type

▣ ALUOut = A op B; // A와 B를 연산한다. op = add, sub, and...

3) Branch

▣ If (A==B) PC = ALUOut;

4. Memory Access or R-Type instuction completion (11:45)

Branch 는 이전 명령에서 다 끝남. 나머지 I type이나 R type 볼 예정

1) I-type > LW

▣ MDR = Memory [ ALUOut ] ; // ALUOut 번째 Memory의 값을 Memory Data Register에 들어가서 저장(업데이트).

2) I-type > SW

▣ Memory [ ALUOut ] = B;

B= rt값임. 그 값을 Store니까 Memory에 Write 하도록 들어가야 한다.

++여기서 생각해봐야 하는 거 (13:34)

B 는 2번째에 업데이트되었음.

하지만 얘네는 Control 신호를 받지 않기 때문에, 매 CLK Cycle에 값이 업데이트됨.

근데 우리는 지금 4번째 CLK 인데 이렇게 연산을 한다는 건 원하는 숫자들로 연산하는 게 아닌 그 뒤에 업데이트된 값으로 하는 게 아닌가?

→ 우리는 B= Rt 값을 Instruction Register값에 의해서 Update 된다. Instruction Register는 바뀌지 않았으므로 같은 값으로 계속 Update가 되므로 문제가 없다!

3) R-type > Add , Sub , and...

Reg [ IR [ 15-11] ] = ALUOut;

ALU연산 결과를 Register File 에 저장하면 됨 → Rd가 가리키는 곳으로 저장하면 됨 = ( IR [15-11])

5. Write-Back step (LW만 여기까지 옴)

Reg [ IR [20 - 16] ] = MDR ;

Memory Data Register에 있는 값을 Register File에 Write 하는 거

LW일 때는 목적지는 Rd가 아닌 Rt로 간다.

출처 : 한동대 SW중심대학

'2학년 2학기 > 컴퓨터 구조' 카테고리의 다른 글

| [ 컴퓨터 구조 ] 9. Pipeline (0) | 2023.07.05 |

|---|---|

| [ 컴퓨터 구조 ] 8. (Multiple Cycle) Multiple Cycle 제어부 (Control Unit) (0) | 2023.07.05 |

| [ 컴퓨터 구조 ] 6. (Multiple Cycle) Multiple Clock Cycle (0) | 2023.07.04 |

| [ 컴퓨터 구조 ] 5. Single Cycle 제어부 (0) | 2023.07.04 |

| [ 컴퓨터 구조 ] 4. Datapath (3) - Instruction Datapath (0) | 2023.06.30 |