오래 못 할 짓 하지 않기

논리 설계 13 (Comparators , Encoder / Decoder ) 본문

Comparators

- Equality (A=B) - 같은지 확인하는 회로 = XNOR

4비트 2진수를 회로로 가져가면

이런 모양이 나온다. 해석해 보자면 같으면 0이 나올 것이다.

그리고 마지막 4input - Nor 게이트에서 모두 0이 들어가야 1이 나옴.

1 = 모두 다 같다는 의미.

이런 모양으로도 구현함. 처음 게이트에서는 같아야 1이 출력되고, 마지막에 And로 곱했을 때 1이 나오면 같다는 뜻.

하나라도 0이 들어오면 다 망함.

- Greater-than & Less-than

예를 드는 게 빠름. A=0 , B=1 이라고 생각하면 A<B이다.

위에 있는 And 게이트에는 A'B가 들어가고, 아래에는 AB'가 들어간다.

우선 위 출력부터 비교해 보자. A'B = (0)' and 1 = 1 and 1이므로 A<B가 성립한다는 의미이다.

반면에 아래 출력으로 보면 AB' = 0 and (1)' = 0 and 0이므로 A>B가 성립하지 않는다는 의미임.

그럼 가운데 게이트로 가보자 (A'B + AB')' = 는 표를 그려오겠다.

보면 이해됨 이하 설명 생략

비트 수가 많아지면 이런 그래프가 연속으로 이어짐

마지막에 들어가는 게이트가 1이 나오면

그 Comparator가 성립한다는 의미

왼쪽에 있는 애들은 이전 비트에서 계산해서 올라온 애들임

이렇게 계산하는 이유는

수가 여러 개인 비트의 크기를 비교할 때, 만약 같은지 확인하는 거면,

한 비트가 같으면 다음 비트 확인하 듯

= 가 1로 출력되어 나간 게 다음 = 으로 계속 가야 하기 때문!

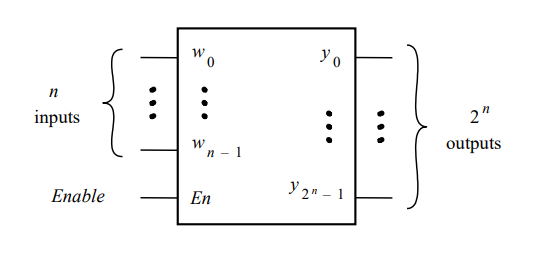

Decoder

디코더는 n개의 입력 이 들어오면

2^n개의 출력 을 하는 회로.

하나의 입력에 하나의 출력만 Active 됨.

ex)- a b --> 01일 때 y1,y3가 1인 상황 X

0 0 y0만 1

0 1 y1만 1

1 0 y2만 1

1 1 y3만 1

Active High Active Low

출력 : 하나만 1 하나만 0

모양새 : Active high에서 마지막 게이트에 inversion 붙은 모양

Enable = Decoder가 작동하도록 하는 신호라고 생각하면 됨.

더 쉽게는 그냥 전원이라 생각해도 됨

En = 0이면 작동 안 함 + 출력은 다 0

En이 En'으로 버블이 달려오는 경우도 있으니 조심!

ㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡㅡ

+ 주로 만들어지는 양상은 Midterm 꼴이다.

문제))

A color plotter has 32 different color pens.

If we use a decoder to select one pen out of the 32, what would the size of the decoder be?

5-to-32 decoder.

이제 디코더를 배웠으니, 비트 수가 많아진 디코더를 생각해 보자.

1. 왼쪽

우선 가장 왼쪽 가운데 있는 Decoder를 보자.

여기에서 출력이 4개이고, 그것들은 다른 Decoder에 있는 En의 입력이 된다.

Decoder 출력 중 하나만 1이고, 나머지는 0이므로 오른쪽에 있는 4개의 Decoder중에서 1개만 작동한다는 의미.

여기에서 가정을 해보자.

w0w1w2w3을 0101로 생각하면,

왼쪽 디코더에서는 (일반적으로) y0 = 00 / y1=01 / y2=10 / y3=11 이므로,

y1만 1로 출력될 것이고, 오른쪽 - 위에서 두 번째 Decoder만 작동할 것이다.

2. 오른쪽

w0w1w2w3가 0101니까 오른쪽 위에서 두 번째 decoder가 작동했고, 그 안에서는 01이 들어왔으니 해당 Decoder의 y1이 출력될 것이므로

결과적으로 y5가 출력될 것이다.

Decoder에서 각각의 출력들은 Minterm으로 표현될 수 있음.

(참고)

x y z

0 0 0 >m0

0 0 1 >m1

0 1 0 >m2

0 1 1 >m3

1 0 0 >m4

1 0 1 >m5

1 1 0 >m6

1 1 1 >m7

문제))

Implementation of a full adder using a 3-to-8 decoder

의 결과인 식을 갖고 만든다.

Encoder

인코더는 2^n개의 입력 이 들어오면

n개의 출력 을 하는 회로.

'인'코더 = 하나의 '인'풋만 1로 '인'식

입력이 다 0이면 NR

1개의 입력만 Active 됨

예)

근데 사실 1개만 active된다기보단 한 개만 알아먹음.

2개 이상 동시에 들어올 경우에 Priority가 가장 높은 놈만 인식함

A0가 가장 낮고, A7로 갈수록 높아짐.

또 다른 표를 보면

출력식 분석 ) X+X'Y = X+Y인 성질을 이용한다.

Z1만 분석해 보자

A7 + A6 + A3 + A2

= ( A7 ) + (A6 A7') + (A3 A'4 A'5 A'6 A'7) + (A2 A'3 A'4 A'5 A'6 A'7) << A3 뒤에 저것들이 0이어야 우선순위를 안 뺏김.

= A7 + A6 + A3 A'4 A'5 A'6 + A2 A'3 A'4 A'5 A'6) A'7 << X+X'Y = X+Y // X = A7 , Y는 저 괄호

= A7 + A6+ (A3 A'4 A'5 + A2 A'3 A'4 A'5 ) A'6 << X+X'Y = X+Y // X = A6 , Y는 저 괄호

= A7 + A6 + (A3 A'4 A'5 + A2 A'3 A'4 A'5 ) <<에서 A'4 A'5로 묶어준다.

= A7 + A6 + (A3 + A2 A'3) * A'4 A'5 << A3 + A2 A'3 은 X+X'Y 꼴로 하면 A3+A2

= A7 + A6 + (A3 + A2) * A'4 A'5

NR : NR = No requests. == input이 다 꺼져있음. Input이 다 0일 때만 , NR = 1

Encoder : NR 출력에서 나타남 (입력이 0일 때)

Decoder : EN 입력(신호)에서 나타남 ( 출력이 0으로 나옴)

(대문자 E는 하나만 가져간다고 생각)

출처 : 한동대학교 고유민교수님 - 논리설계 PPT

'2학년 1학기 > 논리 설계 ( Logic design )' 카테고리의 다른 글

| 논리 설계 15 (PROM PAL PLA) (0) | 2023.04.18 |

|---|---|

| 논리 설계 14 (0) | 2023.04.14 |

| 논리 설계 12 (Carry look ahead adder) (0) | 2023.04.10 |

| 논리 설계 11 (Combinational Logic Circuits = 조합 논리 회로) (0) | 2023.04.05 |

| 논리 설계 10 (콰인 - 맥클러스키 방법 - table , Don't care) ( 사진 안 뜸 ) (0) | 2023.04.04 |