오래 못 할 짓 하지 않기

논리 설계 14 본문

Multiplexer

: 2^n개의 입력과 n개의 선택선으로 인해 1개가 출력 이 되는 구조

입력 : 2^n

선택선 : n

출력 : 1개

위 그림을 봤을 때,

S가 0이면 위 And 게이트에는 1이 들어가고 아래는 0이 들어가기 때문에 둘 중에 하나만 통과

입력이 4(2^2)개일 땐 2개의 control(Select) 입력이 만들어진다.

각각의 Select 입력이 0이면 위에서 들어온 걸 내보내고 , 1이면 밑에서 들어온 걸 내보낸다.

그래서 항상 출력은 1개임

8-to-1 mux = 4-to-1 mux * 2 + enable inputs로 만들 수 있는데, Select 입력은 3개가 아니라 2개로 한다.

4-to-1 mux는 입력선이 2개가 필요한데, 두 개의 mux에 같이 넣고, select하나가 없는 건 En으로 커버하는 느낌임.

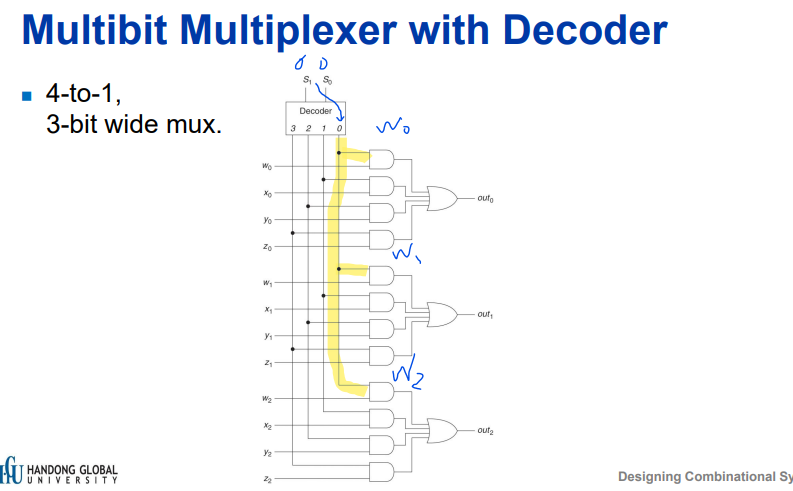

이제 비트 한 자리로 하는 MUX는 다 했으니 비트를 여러 개 만들어보자

Decoder도 같이 쓰이는 Mux.

Decoder의 출력은 1개만 1인 특성을 이용해 and게이트로 통과되는 것들이 out으로 나옴.

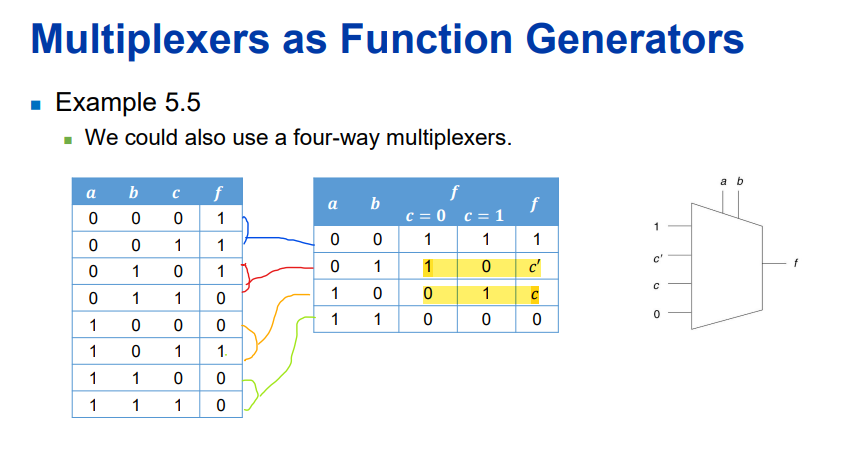

웬만한 함수를 MUX로 바꾸어서

표를 간략화 할 수도 있고

오른쪽 표로 만들면 훨씬 간단한 회로를 만들 수 있다고 함.

f(x,y,z) 함수를 MUX로 바꿀 수도 있다.

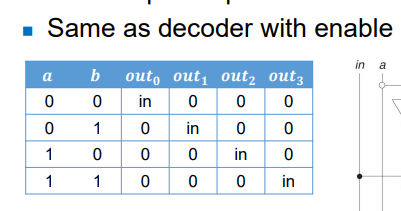

Demultiplexer (Demux)

: 1개의 입력과 n개의 선택선으로 인해 2^n개가 출력 이 되는 구조

입력 : 1개

선택선 : n

출력 : 2^n개

선택선의 조합에 따라 들어온 출력되는 선이 다르다.

여기에서도 En이 쓰이는데, En이 1이면 정상적으로 작동하고,

En이 0일 땐, Z(zero reaction)으로 회로가 연결되어있지 않은 것(open circuit)처럼 작동하지 않는다.

En이 0이면 a로 올라가면서 1이 되고, a는 작동하며 , b로는 0이 들어가 작동하지 않을 것.

En = 0 일 땐, F = a

반대로 En = 1이면 a로는 0이 들어가고 , b로는 1이 들어가서 b쪽으로만 작동한다.

En = 1 일 땐, F = b

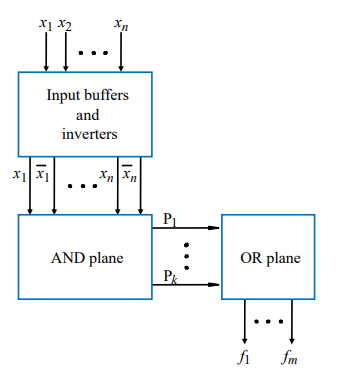

Gate Array

: 복잡한 시스템을 빨리 구현하기 위해 사용한다고 함

쓰이는 매커니즘은 이러하다.

1. 입력을 그대로 받고, Inversion으로도 받아놓고 옆으로 배열해놓음

2. 그것들을 필요한 조합으로 And 게이트에 넣는다. (P1부터 Pk까지)

3. 거기에서 필요한 조합으로 Or 게이트에 넣는다. (F1부터 Fm까지)

𝑓 = 𝑎 ′𝑏 ′ + 𝑎𝑏𝑐

𝑔 = 𝑎 ′𝑏 ′ 𝑐 ′ + 𝑎𝑏 + 𝑏𝑐

ℎ = 𝑎 ′𝑏 ′ + 𝑐

중요한 건 실선만 신경쓰면 됨!! 점선은 무시하셈

점선 : 연결될 가능성이 있음

개선된 버전

X표시가 있는 건 이게 같은 선에 있는 게이트로 Connection이 될 거다.

출처 : 한동대학교 고윤민 교수님 - 논리설계 PPT

'2학년 1학기 > 논리 설계 ( Logic design )' 카테고리의 다른 글

| 논리 설계 16 (순차 논리 회로 , SR latch, D latch) (0) | 2023.04.25 |

|---|---|

| 논리 설계 15 (PROM PAL PLA) (0) | 2023.04.18 |

| 논리 설계 13 (Comparators , Encoder / Decoder ) (0) | 2023.04.11 |

| 논리 설계 12 (Carry look ahead adder) (0) | 2023.04.10 |

| 논리 설계 11 (Combinational Logic Circuits = 조합 논리 회로) (0) | 2023.04.05 |