오래 못 할 짓 하지 않기

논리 설계 15 (PROM PAL PLA) 본문

PROM (Programmable Read-Only Memory)

>> AND = Fixed ( Decoder) / OR = Programmable

PROM은

1. 고정된 " AND " array 들

2. 내가 마음대로 입력을 설정할 수 있는( programmable = 변경 가능한 ) OR array

로 구성되어 있다.

+ AND가 디코더로 구현됨

* Fixed된 AND가 Decoder로 구현되면서 필요할만한 minterm들은 다 제공됨 ,

OR로 우리가 필요에 맞게 가져가면 되는 거임

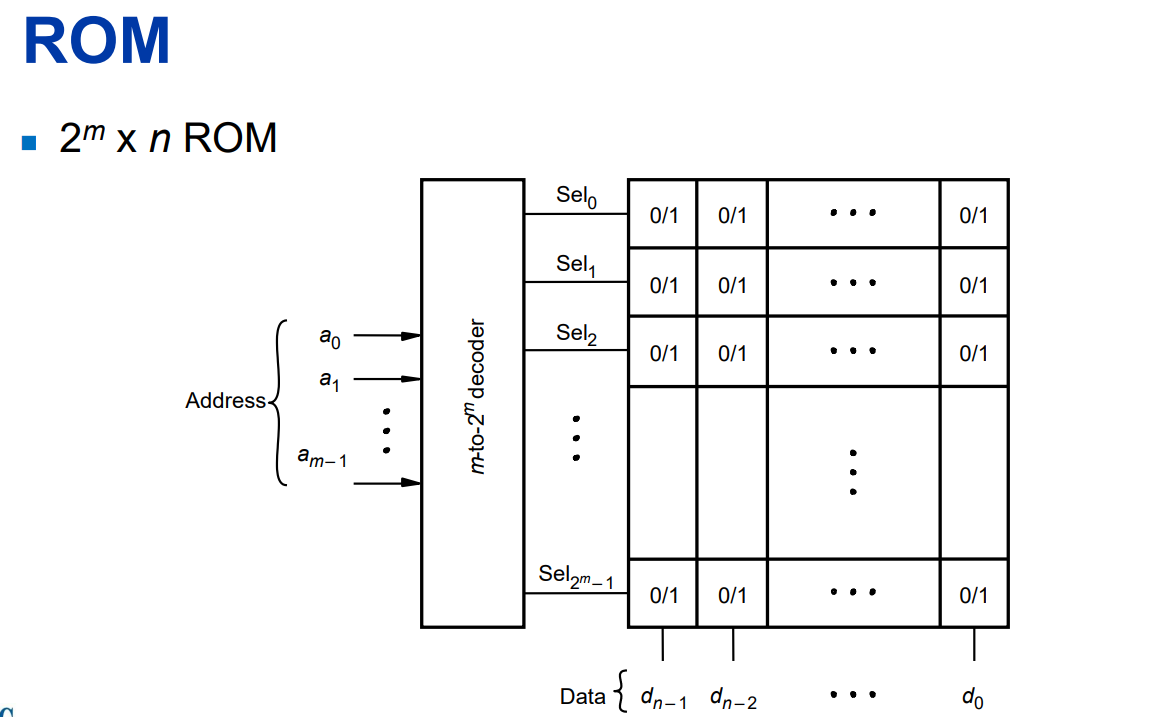

- 입력 : m개의 입력이 들어감

- 중간 단계 : AND( = Decoder ) 를 통해 m개가 2^m개로 늘어남

그렇게 만들어진 Minterm들을 programmable한 OR 게이트로 원하는 결과 출력

- 분석

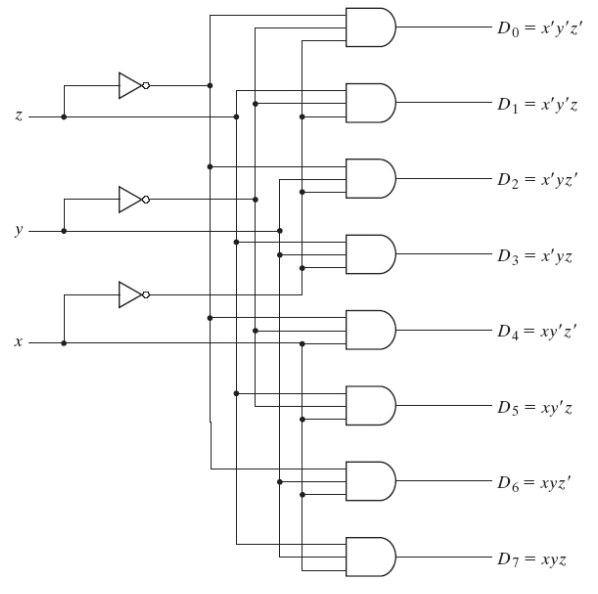

(왼쪽) Decoder를 저렇게 크게 분해하면 저런 형식이 나온다.

4개의 입력가 들어온 후에 / 2^4 개의 minterm들이 AND를 거쳐서 나오게 된다.

(Fixed And임 <<내가 어떻게 뭐뭐 가져오는 거 못 함 근데 그래도 다 있음)

(오른쪽) And로 넘어온 것들 중에 필요한 minterm들은 OR로 가져온다.

- 추가 설명

Decoder를 쓰면 Fixed and라도 엥간한 경우의 수 다 나오니까 걱정 ㄴ

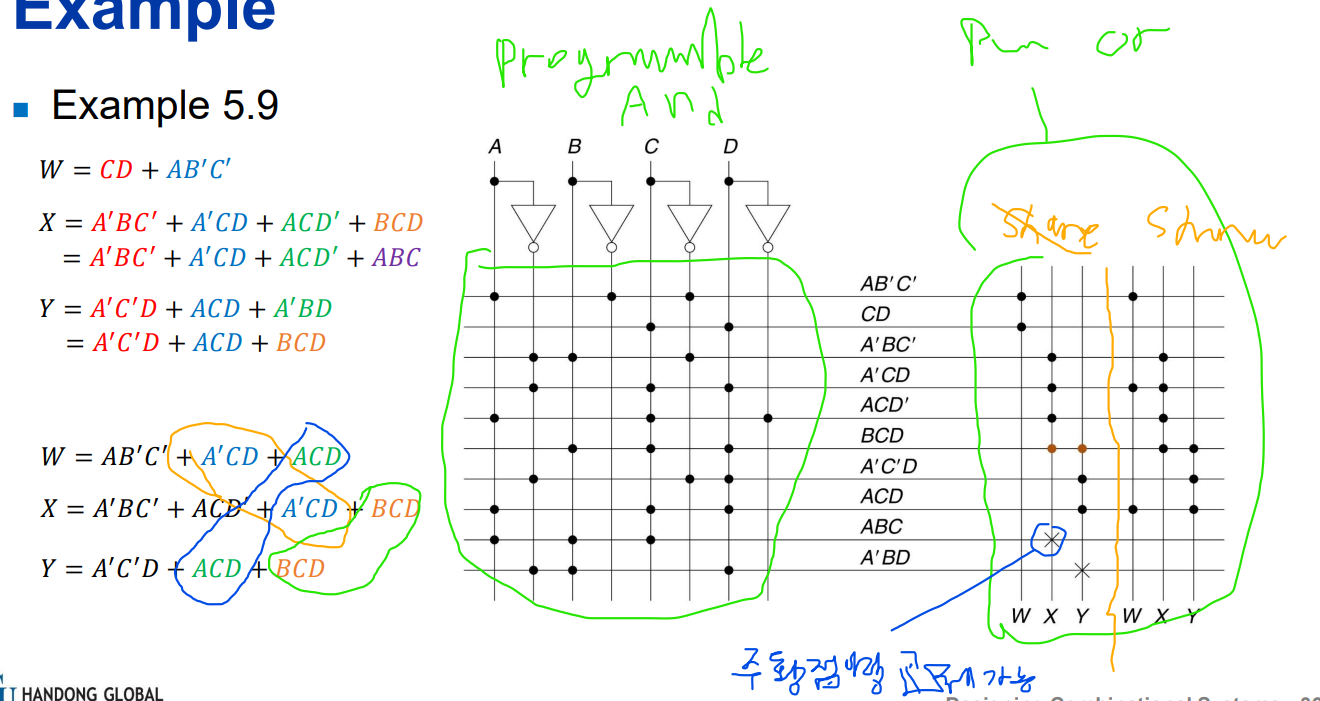

PLA (Programmable Logic Array)

>> AND , OR 둘 다 Programmable

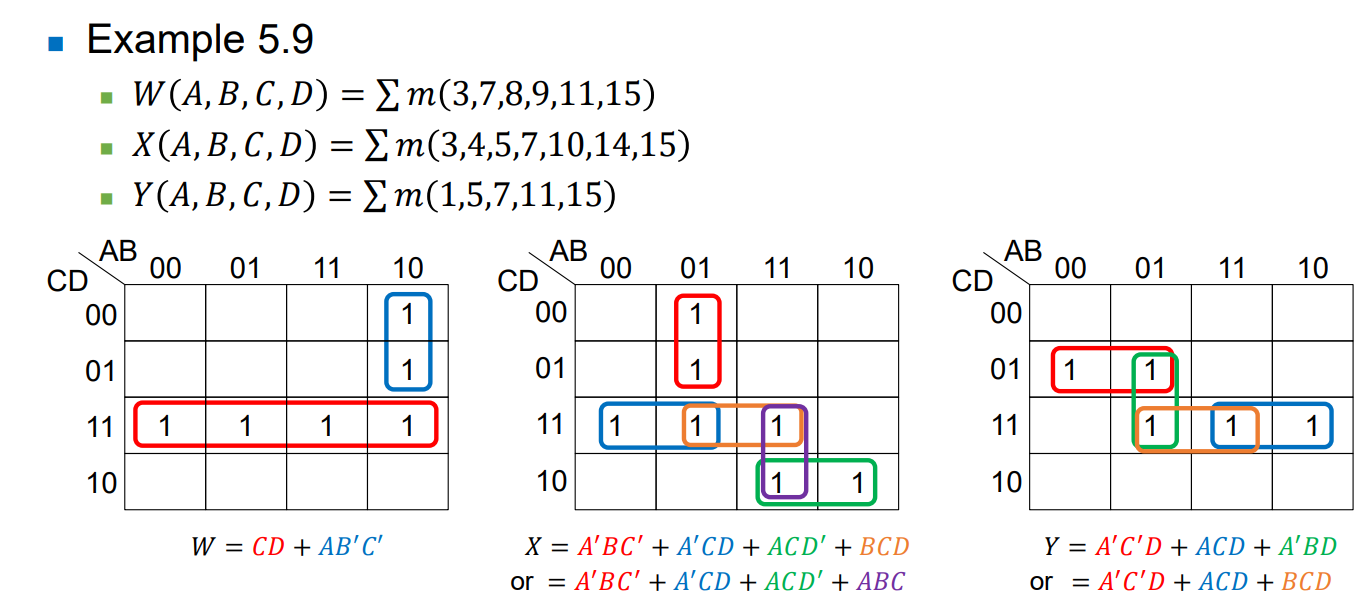

PLA에 쓸 SOP들을 찾는다.

(다른 건 다 늘어뜨려놓고 골랐는데 이건 내가 선택 가능하기 때문에 최대한 게이트 적게 쓰려고 ㅇㅇ)

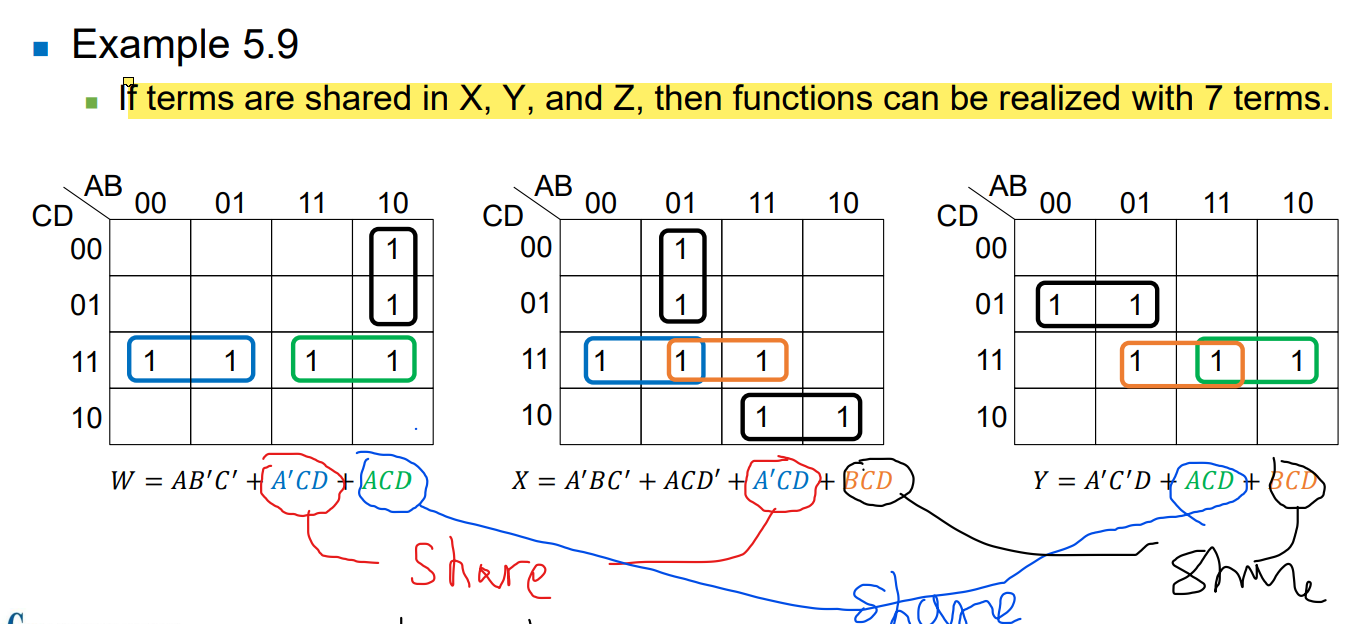

==> 방법 : 카르노 맵에 각 식을 그린 다음, 공통으로 묶이는 곳들이 있으면 share함으로써 게이트 수를 줄일 수 있다.

옆에 세 식을 보면 카르노맵을 이렇게 그릴 수 있다. 하지만 이렇게 그렸을 경우에는 공유하는 항이

X식과 Y식에서 BCD밖에 없어서 게이트가 최대 9개(공유하면 8개)가 나오게 된다.

같은 자리에 있는 건 최대한 공유하려고 했을 때는 항을 9개에서 7개로 줄였고, 이 덕분에 게이트의 수도 7개로 줄임

이렇게 만들어진 식을 회로로 그렸을 때는 다음과 같다.

- 분석

(왼쪽) 우선 PROM과 비교했을 때, 쓸데없는 항들이 줄어들었다.

똑같이 4input인데, And를 거쳐 나가는 건 10개다. (공유하면 7개)

(오른쪽) Share 전을 보면, 10개가 있고 W는 2개밖에 없다.

Share 후에는, 7개가 있고, 대신 W가 공유를 하기 위해 1개가 늘어났음.

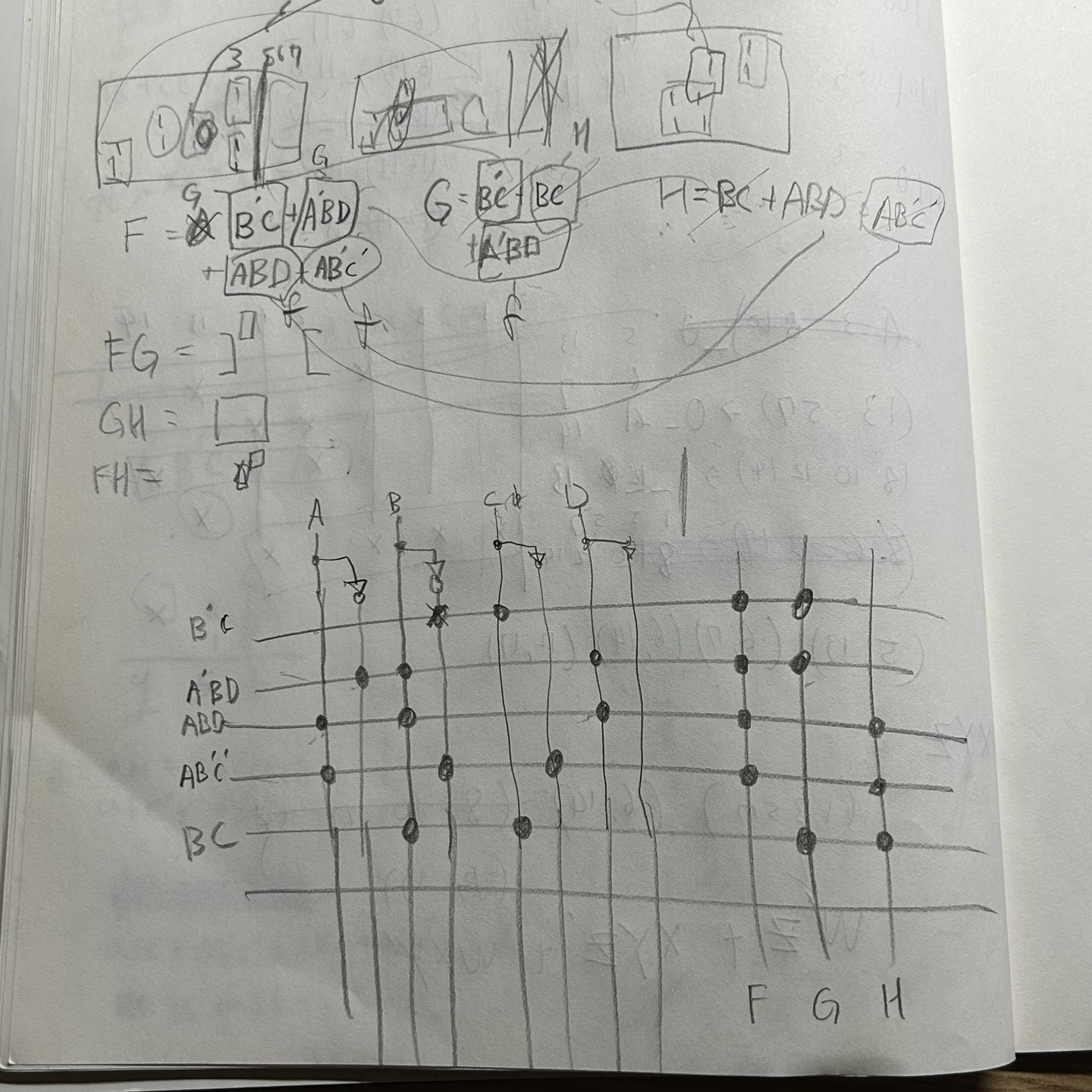

PAL (Programmable Array Logic)

>> AND는 Programmable , OR은 Fixed

- OR로 나가는 것들이 고정되어 있으므로, 어떤 걸 OR로 줄 지 AND에서 정할 수 있다.

- And gate는 주로 공유하지 않는다고 함.

ex) 밑에 사진으로는 W로 가기 OR 전 AND에서 나온 AB'C'가 만약 다른 곳에 있더라도 굳이 주러 안 감.

출처 : 한동대학교 고윤민교수님 - 논리설계 PPT

'2학년 1학기 > 논리 설계 ( Logic design )' 카테고리의 다른 글

| 논리 설계 17 (Flip-Flop) (0) | 2023.04.30 |

|---|---|

| 논리 설계 16 (순차 논리 회로 , SR latch, D latch) (0) | 2023.04.25 |

| 논리 설계 14 (0) | 2023.04.14 |

| 논리 설계 13 (Comparators , Encoder / Decoder ) (0) | 2023.04.11 |

| 논리 설계 12 (Carry look ahead adder) (0) | 2023.04.10 |